## MG32F04P032 Arm<sup>®</sup>Cortex<sup>®</sup> M0 Core

# User Guide

Version 1.00 Date 2025/03/03

This document contains information on a new product under development by Megawin. Megawin reserves the right to change or discontinue this product without notice. © Megawin Technology Co., Ltd. 2025 All rights reserved.

S D

## Contents

| Contents |       |              |                                                                   |    |  |

|----------|-------|--------------|-------------------------------------------------------------------|----|--|

| Fig      | gures | 5            |                                                                   | 12 |  |

| Tables   |       |              |                                                                   |    |  |

| 1        |       | System       | n and Memory Architecture                                         | 17 |  |

|          | 1.1   |              | System architecture overview                                      |    |  |

|          |       | 1.1.1        | System bus                                                        | 17 |  |

|          |       | 1.1.2        | DMA bus                                                           | 17 |  |

|          |       | 1.1.3        | BUS matrix                                                        |    |  |

|          | 1.2   |              | Memory introduction                                               |    |  |

|          |       | 1.2.1        | Memory map and register addressing                                |    |  |

|          |       | 1.2.2        | Embedded SRAM                                                     | 19 |  |

|          |       | 1.2.3        | FLASH memory overview                                             | 19 |  |

|          |       | 1.2.4        | Boot configuration                                                | 20 |  |

|          |       | 1.2.5        | Boot loader                                                       | 20 |  |

| 2        |       | Embed        | lded FLASH                                                        | 21 |  |

|          | 2.1   |              | Overview                                                          | 21 |  |

|          | 2.2   |              | Flash composition and description                                 | 21 |  |

|          |       | 2.2.1        | Flash composition                                                 |    |  |

|          |       | 2.2.2        | Option byte description                                           |    |  |

|          |       | 2.2.3        | IAP/Data space description                                        | 23 |  |

|          | 2.3   |              | Flash option and procedure                                        | 23 |  |

|          |       | 2.3.1        | Flash read operation                                              | 23 |  |

|          |       | 2.3.2        | Flash programming mode and operation procedure                    | 24 |  |

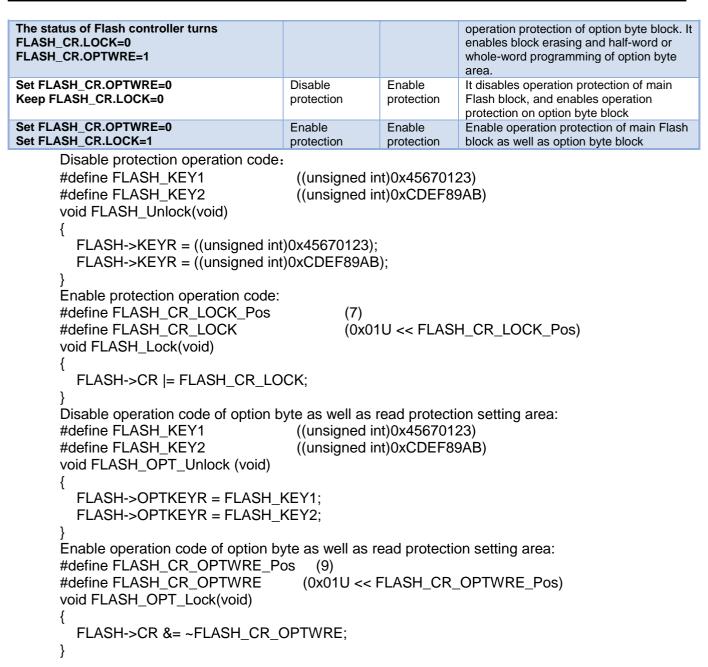

|          |       | 2.3.3        | Disable and enable the operation restriction on Flash block       | 27 |  |

|          |       | 2.3.4        | Disable and enable the operation restriction on option byte block | 27 |  |

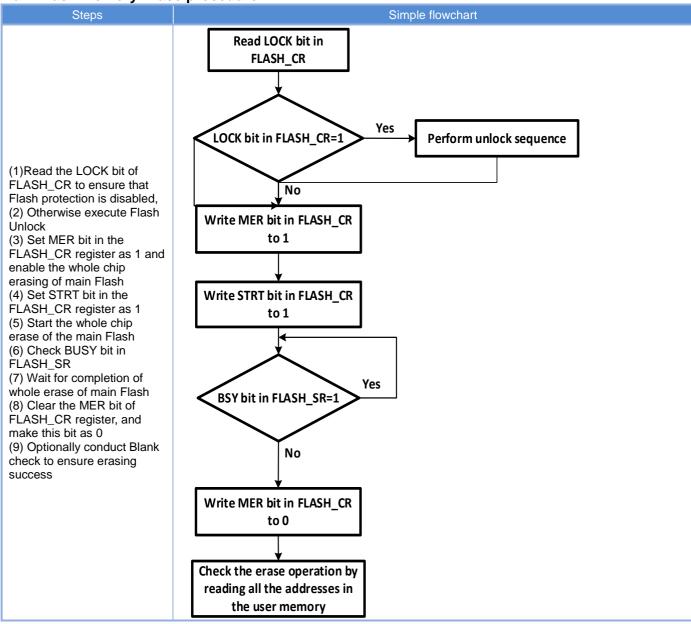

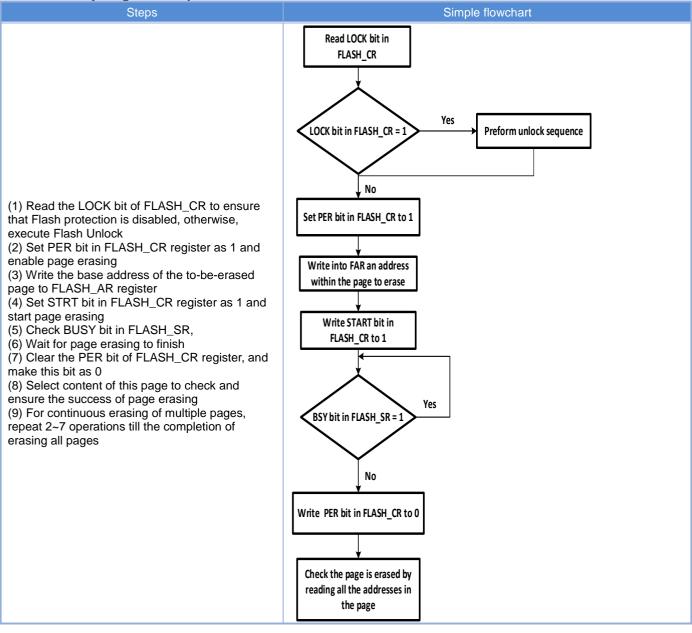

|          |       | 2.3.5        | Main Flash block erasing                                          |    |  |

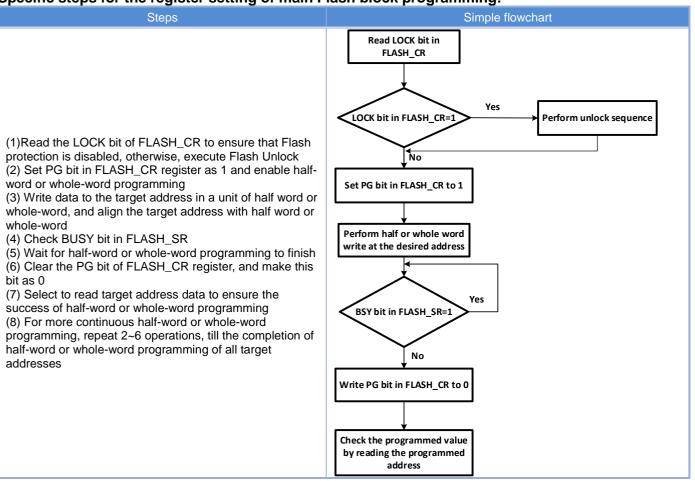

|          |       | 2.3.6        | Main Flash block programming                                      |    |  |

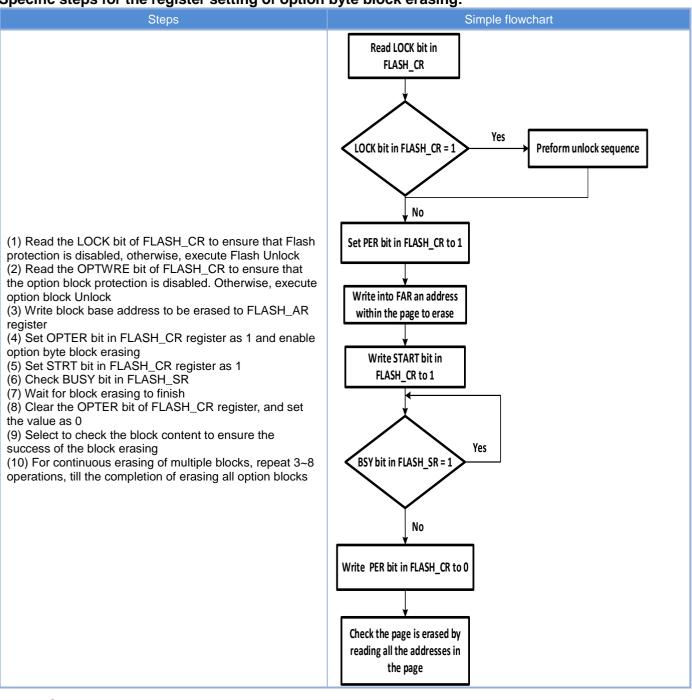

|          |       | 2.3.7        | Option byte block erasing                                         |    |  |

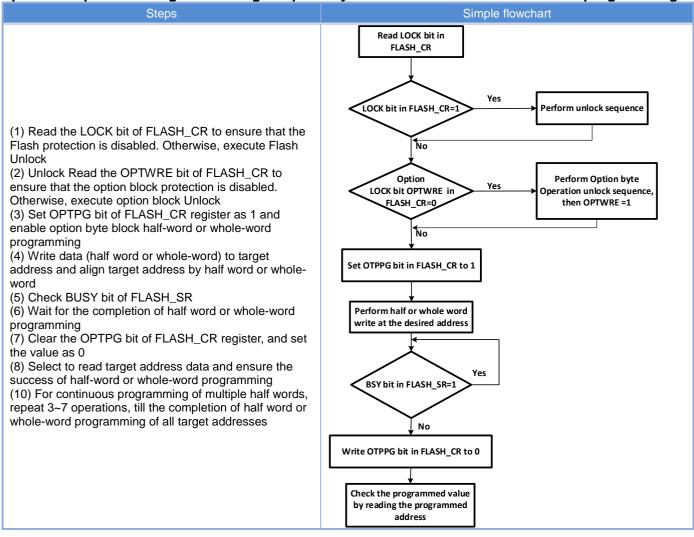

|          |       | 2.3.8        | Option byte block programming                                     |    |  |

|          |       | 2.3.9        | Flash memory protection                                           |    |  |

|          | 2.4   |              | Register                                                          |    |  |

|          |       | 2.4.1        | Register overview                                                 |    |  |

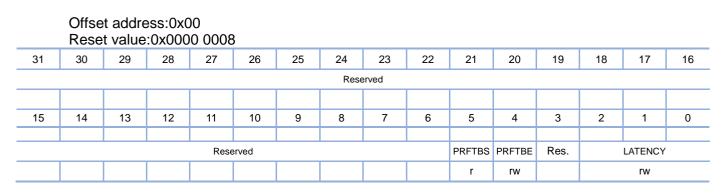

|          |       | 2.4.2        | FLASH_ACR Flash Access Control Register                           |    |  |

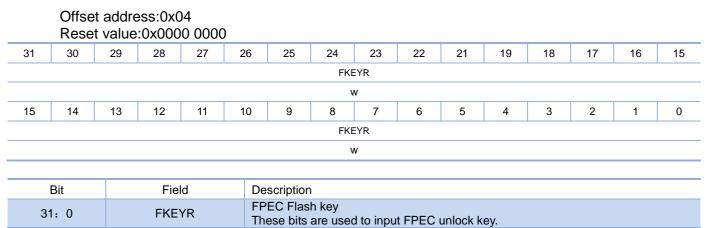

|          |       | 2.4.3        | FLASH_KEYR FPEC Key Register                                      |    |  |

|          |       | 2.4.4        | FLASH_OPTKEYR Flash OPTKEY Register                               |    |  |

|          |       | 2.4.5        | FLASH_SR Flash Status Register                                    |    |  |

|          |       | 2.4.6        | FLASH_CR Flash Control Register                                   |    |  |

|          |       | 2.4.7        | FLASH_AR Flash Address Register                                   |    |  |

|          |       | 2.4.8        | FLASH_OBR Option Byte Register                                    |    |  |

|          |       | 2.4.9        | FLASH_WRPR Write Protection Register                              |    |  |

| 3        |       | PWR P        | ower Controller                                                   |    |  |

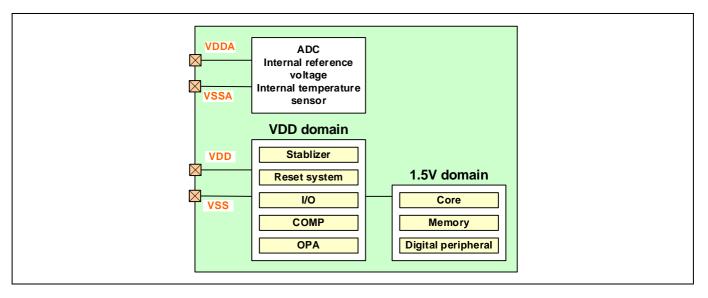

|          | 3.1   |              | Power supply system                                               |    |  |

|          |       | 3.1.1        | Analog module power supply                                        |    |  |

|          |       | 3.1.2        | Digital module power supply                                       |    |  |

|          |       | 3.1.3        | VDD domain                                                        |    |  |

|          |       | 3.1.4        | 1.5V domain                                                       |    |  |

|          | 3.2   | 0 0 <i>i</i> | Power manager                                                     |    |  |

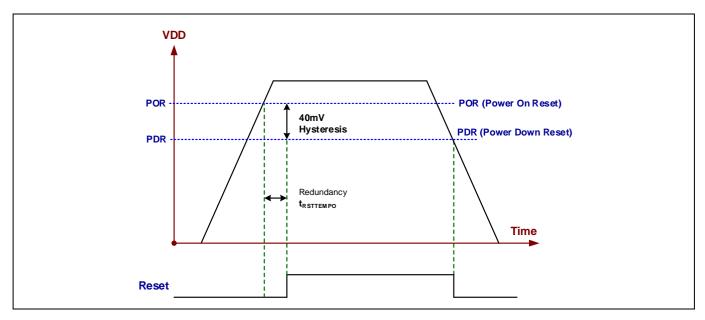

|          |       | 3.2.1        | Power on reset and power down reset                               |    |  |

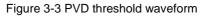

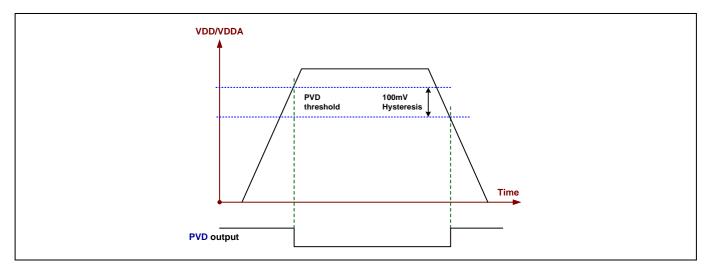

|          | ~ ~   | 3.2.2        | Programmable voltage detector                                     |    |  |

|          | 3.3   | 0.04         | Power control                                                     |    |  |

|          |       | 3.3.1        | Power control overview                                            |    |  |

|   |             | 3.3.2          | Reducing system clock under run mode                       |    |

|---|-------------|----------------|------------------------------------------------------------|----|

|   |             | 3.3.3          | External clock control                                     |    |

|   |             | 3.3.4          | Sleep mode                                                 |    |

|   |             | 3.3.5          | Stop Mode                                                  |    |

|   | 3.4         |                | Register                                                   |    |

|   |             | 3.4.1          | PWR_CR Power Control Register                              |    |

|   |             | 3.4.2          | PWR_CSR Power Control/Status Register                      |    |

|   |             | 3.4.3          | PWR_CFGR Power Configuration Register                      |    |

| _ |             | 3.4.4          | PWR_MEMCR Power Memory Control Register                    |    |

| 4 |             | RCC CI         | ocks and Reset                                             |    |

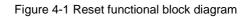

|   | 4.1         |                | Reset unit                                                 |    |

|   |             | 4.1.1          | Introduction                                               |    |

|   |             | 4.1.2          | Functional block diagram                                   |    |

|   |             | 4.1.3          | Main features                                              |    |

|   | 4.0         | 4.1.4          | Functional description                                     |    |

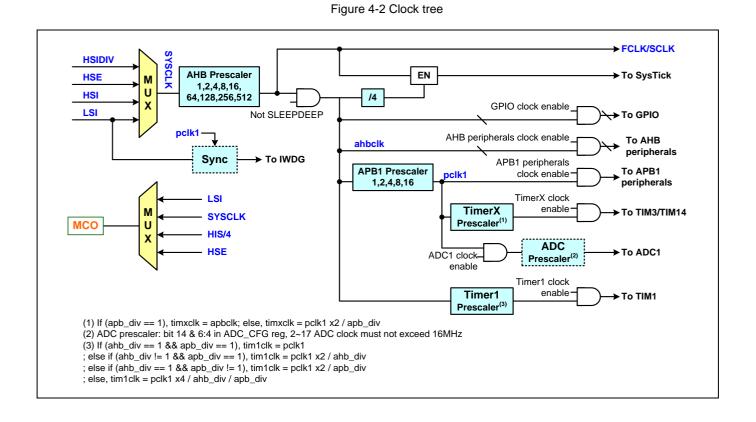

|   | 4.2         | 4.2.1          | Clock unit                                                 |    |

|   |             | 4.2.1          |                                                            |    |

|   |             | 4.2.2<br>4.2.3 | Functional block diagram                                   |    |

|   |             | 4.2.3<br>4.2.4 | Functional description                                     |    |

|   | 4.3         | 4.2.4          | Register                                                   |    |

|   | 4.3         | 4.3.1          | Overview of registers                                      |    |

|   |             | 4.3.1          | RCC_CR clock control register                              |    |

|   |             | 4.3.2          | RCC_CFGR clock configuration register                      |    |

|   |             | 4.3.4          | RCC_CIR clock torniguration register                       |    |

|   |             | 4.3.5          | RCC_AHBRSTR AHB peripheral reset register                  |    |

|   |             | 4.3.6          | RCC_APB1RSTR APB1 peripheral reset register                |    |

|   |             | 4.3.7          | RCC_AHBENR AHB peripheral clock enable register            |    |

|   |             | 4.3.8          | RCC_APB1ENR APB1 peripheral clock enable register          |    |

|   |             | 4.3.9          | RCC_CSR control status register                            |    |

| 5 |             |                | G System Controller                                        |    |

| 5 | 5.1         | 515CF          | Introduction                                               |    |

|   | 5.1<br>5.2  |                | Register                                                   |    |

|   | <b>5.</b> Z | 5.2.1          | Register overview                                          |    |

|   |             | 5.2.1<br>5.2.2 | SYSCFG_CFGR Configuration Register                         |    |

|   |             | 5.2.2<br>5.2.3 | SYSCFG_EXTICR1 External Interrupt Configuration Register 1 |    |

|   |             | 5.2.3<br>5.2.4 | SYSCFG_EXTICR2 External Interrupt Configuration Register 2 |    |

|   |             | 5.2.5          | SYSCFG_EXTICR3 External Interrupt Configuration Register 3 |    |

|   |             | 5.2.6          | SYSCFG_EXTICR4 External Interrupt Configuration Register 4 |    |

| 6 |             |                | Hardware Divider                                           |    |

| 0 | 6.1         |                | Overview                                                   |    |

|   | 6.2         |                | Main characteristics                                       |    |

|   | 6.3         |                | Functional description                                     |    |

|   | 6.4         |                | Register                                                   |    |

|   | 0.1         | 6.4.1          | Overview of registers                                      |    |

|   |             | 6.4.2          | HWDIV_DVDR Dividend Register                               |    |

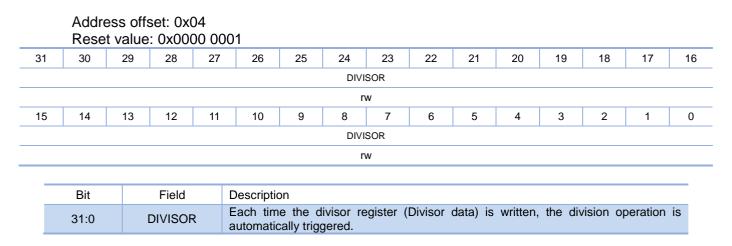

|   |             | 6.4.3          | HWDIV_DVSR Divisor Register                                |    |

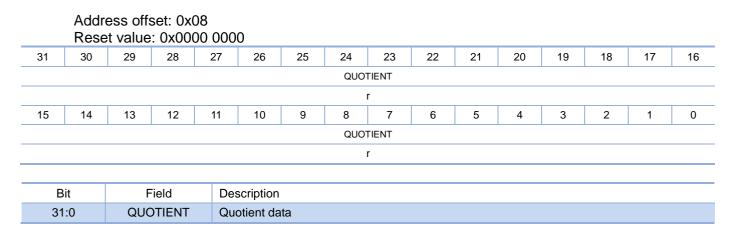

|   |             | 6.4.4          | HWDIV_QUOTR Quotient Register                              |    |

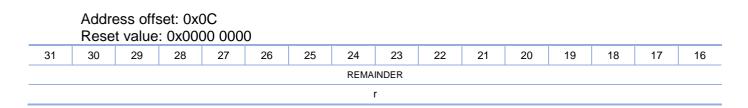

|   |             | 6.4.5          | HWDIV_RMDR Remainder Register                              |    |

|   |             | 6.4.6          | HWDIV_SR Status Register                                   |    |

|   |             | 6.4.7          | HWDIV_CR Control Register                                  |    |

| 7 |             | EXTI In        | terrupt and Event                                          | 67 |

| • | 7.1         | _/\\\          | Introduction                                               |    |

|   |             |                |                                                            |    |

|   | 7.2 |        | Main characteristics                                        | 67 |

|---|-----|--------|-------------------------------------------------------------|----|

|   | 7.3 |        | Function description                                        | 67 |

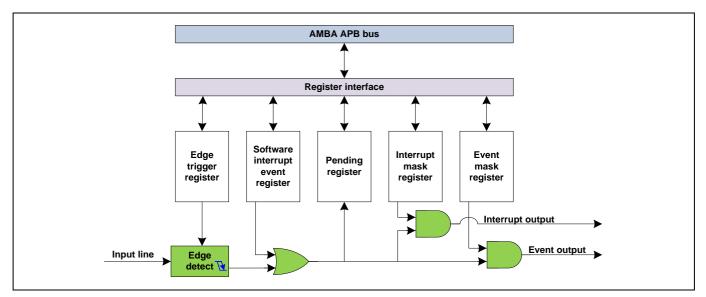

|   |     | 7.3.1  | Function block diagram                                      | 67 |

|   |     | 7.3.2  | Interrupt and anomaly vector                                | 68 |

|   |     | 7.3.3  | Wake-up event management                                    | 69 |

|   |     | 7.3.4  | Interrupt function description                              | 69 |

|   |     | 7.3.5  | Hardware interrupt output                                   | 69 |

|   |     | 7.3.6  | Hardware event output                                       | 69 |

|   |     | 7.3.7  | Software interrupt and event output                         | 70 |

|   |     | 7.3.8  | External interrupt mapping                                  | 70 |

|   | 7.4 |        | Register                                                    | 70 |

|   |     | 7.4.1  | Register overview                                           | 70 |

|   |     | 7.4.2  | EXTI_IMR Interrupt Mask Register                            | 71 |

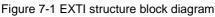

|   |     | 7.4.3  | EXTI_EMR Event Mask Register                                | 71 |

|   |     | 7.4.4  | EXTI_RTSR Rising Edge Trigger Selection Register            | 71 |

|   |     | 7.4.5  | EXTI_FTSR Falling Edge Trigger Selection Register           | 72 |

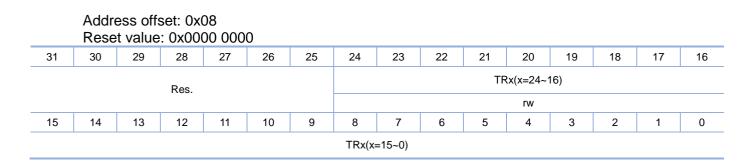

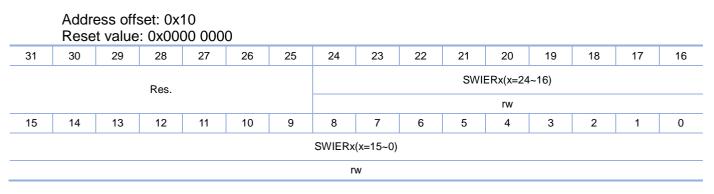

|   |     | 7.4.6  | EXTI_SWIER Software Interrupt Event Register                | 72 |

|   |     | 7.4.7  | EXTI_PR Software Interrupt Event Pending Register           | 72 |

| 8 |     |        | irect Memory Access Controller                              |    |

| - | 8.1 |        | Overview                                                    |    |

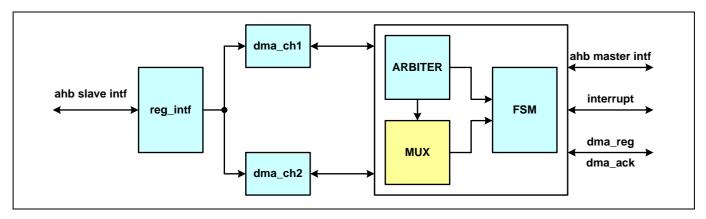

|   | 8.2 |        | DMA functional block diagram                                |    |

|   | 8.3 |        | Main characteristics                                        |    |

|   | 8.4 |        | Interrupt                                                   | 75 |

|   | 8.5 |        | DMA                                                         |    |

|   |     | 8.5.1  | DMA request mapping                                         | 75 |

|   | 8.6 |        | Functional description                                      | 76 |

|   |     | 8.6.1  | DMA transactions                                            | 76 |

|   |     | 8.6.2  | Arbiter                                                     | 76 |

|   |     | 8.6.3  | DMA channels                                                | 77 |

|   |     | 8.6.4  | Programmable data width, data alignment and endian          | 78 |

|   |     | 8.6.5  | Error management                                            | 79 |

|   | 8.7 |        | DMA register description                                    | 80 |

|   |     | 8.7.1  | DMA_ISR DMA Interrupt Status Register                       | 80 |

|   |     | 8.7.2  | DMA_IFCR DMA Interrupt Flag Clear Register                  | 80 |

|   |     | 8.7.3  | DMA_CCRx DMA Channel x Configuration Register (x=1~2)       | 81 |

|   |     | 8.7.4  | DMA_CNDTRx DMA Channel x Number of Data Register (x=1~2)    |    |

|   |     | 8.7.5  | DMA_CPARx DMA Channel x Peripheral Address Register (x=1~2) | 83 |

|   |     | 8.7.6  | DMA_CMARx DMA Channel x Memory Address Register (x=1~2)     |    |

| 9 |     | GPIO G | General-Purpose I/Os                                        |    |

| - | 9.1 |        | Overview                                                    |    |

|   | 9.2 |        | Main characteristics                                        |    |

|   | 9.3 |        | Functional description                                      |    |

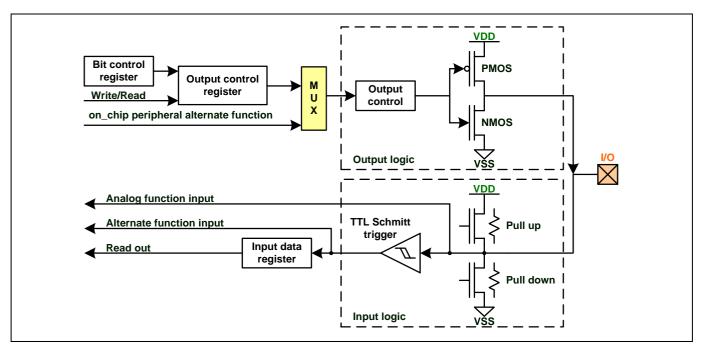

|   |     | 9.3.1  | Functional block diagram                                    |    |

|   |     | 9.3.2  | GPIO port configuration                                     |    |

|   |     | 9.3.3  | Alternate function                                          |    |

|   |     | 9.3.4  | GPIO locking mechanism                                      |    |

|   |     | 9.3.5  | Input configuration                                         |    |

|   |     | 9.3.6  | Output configuration                                        |    |

|   |     | 9.3.7  | Alternate function configuration                            |    |

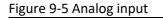

|   |     | 9.3.8  | Analog input configuration                                  |    |

|   |     | 9.3.9  | External clock used as alternate GPIO port                  | 89 |

|   |     | 9.3.10 | SWD alternate function remapping                            |    |

|   | 9.4 |        | Register                                                    |    |

|   |     | 9.4.1  | Overview of registers                                       | 89 |

|    |      | 9.4.2              | GPIOx_CRL Port Configuration Register Low                           | 89    |

|----|------|--------------------|---------------------------------------------------------------------|-------|

|    |      | 9.4.3              | GPIOx_CRH Port Configuration Register High                          | 90    |

|    |      | 9.4.4              | GPIOx_IDR Port Input Data Register                                  |       |

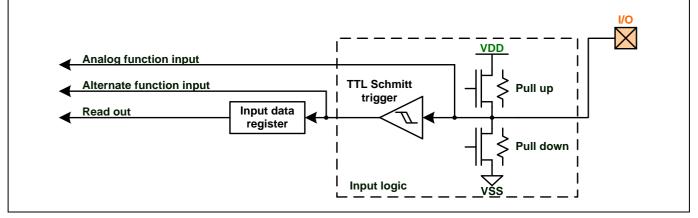

|    |      | 9.4.5              | GPIOx_ODR Port Output Data Register                                 | 91    |

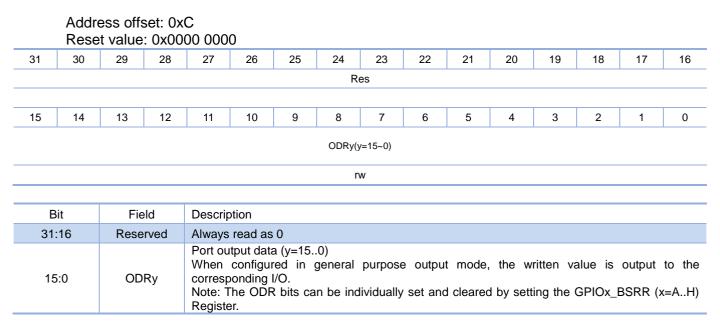

|    |      | 9.4.6              | GPIOx_BSRR Port Bit Set/Reset Register                              | 91    |

|    |      | 9.4.7              | GPIOx_BRR Port Bit Reset Register                                   | 92    |

|    |      | 9.4.8              | GPIOx_LCKR Port Configuration Lock Register                         | 92    |

|    |      | 9.4.9              | GPIOx_DCR Port Output Open Drain Control Register                   | 92    |

|    |      | 9.4.10             | GPIOx_AFRL Port Alternate Function Register Low                     | 93    |

|    |      | 9.4.11             | GPIOx_AFRH Port Alternate Function Register High                    | 93    |

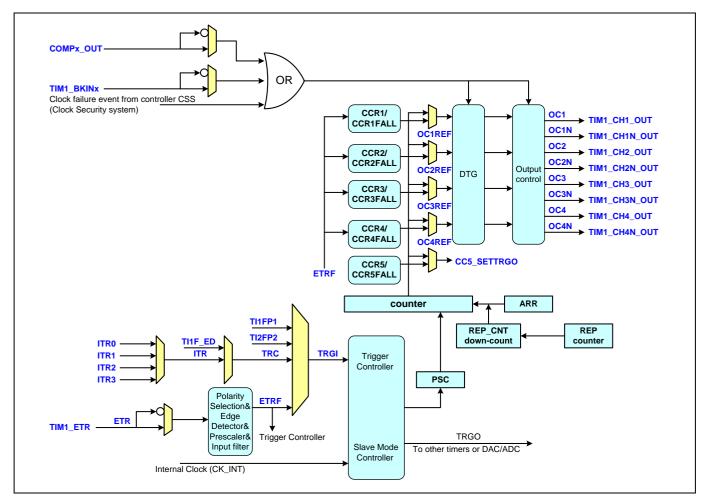

| 10 |      | TIM1 Ac            | Ivanced Timer                                                       | 94    |

|    | 10.1 |                    | Overview                                                            | 94    |

|    | 10.2 |                    | Function block diagram                                              | 94    |

|    | 10.3 |                    | Main characteristics                                                | 95    |

|    | 10.4 |                    | Function description                                                | 95    |

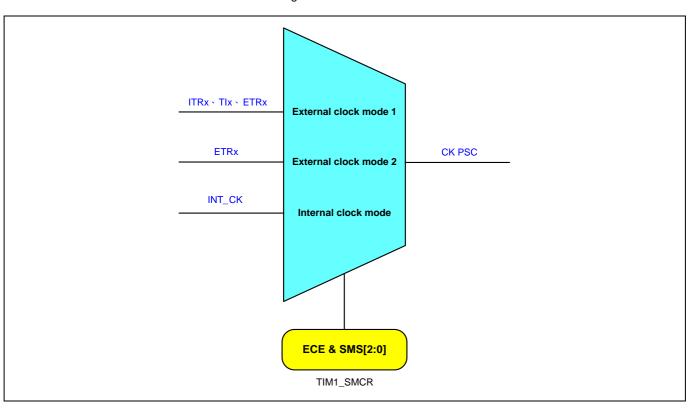

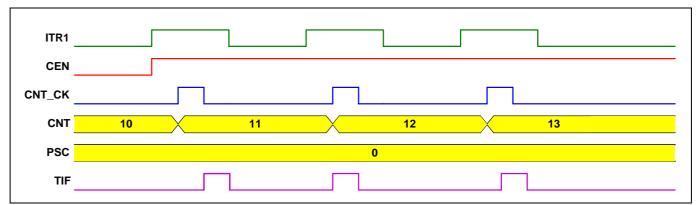

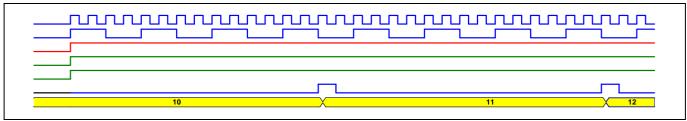

|    |      | 10.4.1             | Clock                                                               | 95    |

|    |      | 10.4.2             | Repeat counter                                                      | . 101 |

|    |      | 10.4.3             | Output compare                                                      | . 102 |

|    |      | 10.4.4             | Slave mode                                                          | . 113 |

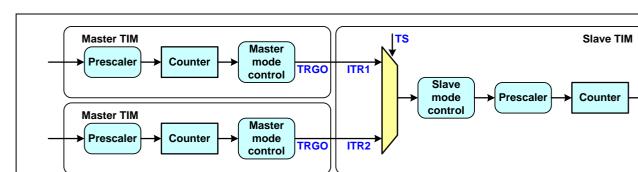

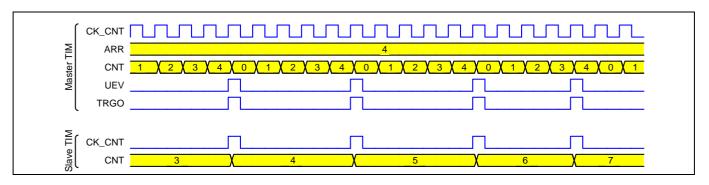

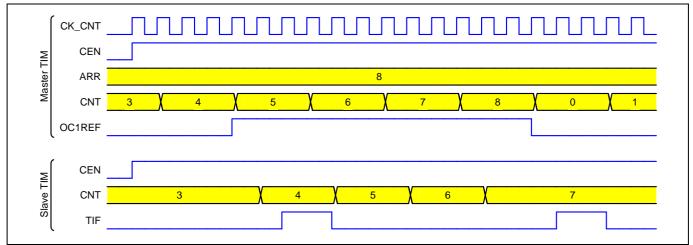

|    |      | 10.4.5             | Timer synchronization                                               | . 115 |

|    |      | 10.4.6             | Debug mode                                                          | . 117 |

|    |      | 10.4.7             | Interrupt                                                           |       |

|    |      | 10.4.8             | DMA                                                                 |       |

|    | 10.5 |                    | Register                                                            |       |

|    |      | 10.5.1             | TIM1_CR1 Control Register 1                                         |       |

|    |      | 10.5.2             | TIM1_CR2 Control Register 2                                         |       |

|    |      | 10.5.3             | TIM1_SMCR Slave Mode Control Register                               |       |

|    |      | 10.5.4             | TIM1_DIER DMA/Interrupt Enable Register                             |       |

|    |      | 10.5.5             | TIM1_SR Status Register                                             |       |

|    |      | 10.5.6             | TIM1_EGR Event Generation Register                                  |       |

|    |      | 10.5.7             | TIM1_CCMR1 Compare Mode Register 1                                  |       |

|    |      | 10.5.8             | TIM1_CCMR2 Compare Mode Register 2                                  |       |

|    |      | 10.5.9             | TIM1_CCER Compare Enable Register                                   |       |

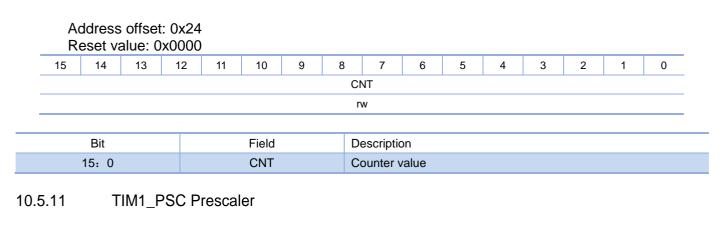

|    |      | 10.5.10            | TIM1_CNT Counter                                                    |       |

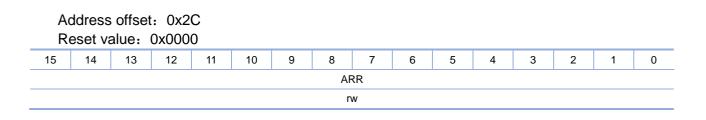

|    |      | 10.5.11<br>10.5.12 | TIM1_PSC Prescaler<br>TIM1_ARR Auto Reload Register                 |       |

|    |      | 10.5.12            | -                                                                   |       |

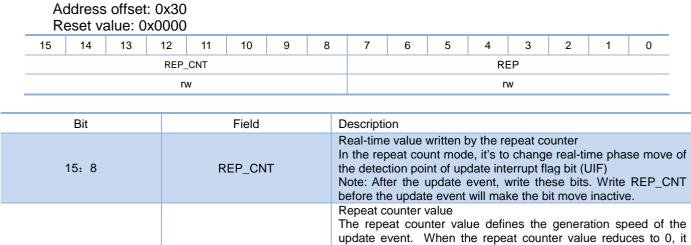

|    |      | 10.5.13            | TIM1_RCR Repeat Count Register                                      |       |

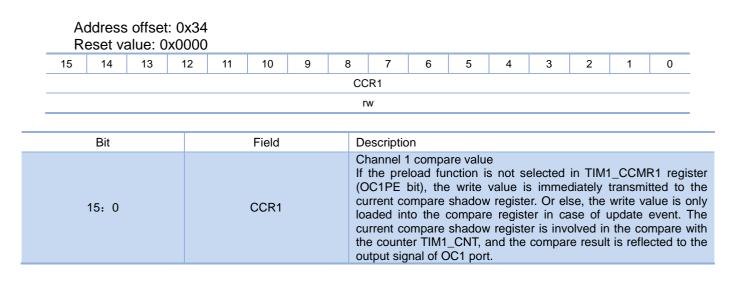

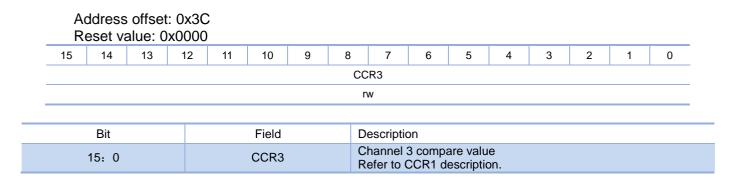

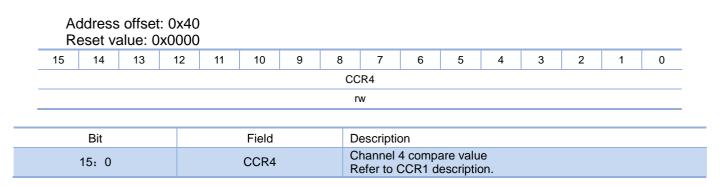

|    |      | 10.5.14            | TIM1_CCR1 Compare Register 1<br>TIM1_CCR2 Compare Register 2        |       |

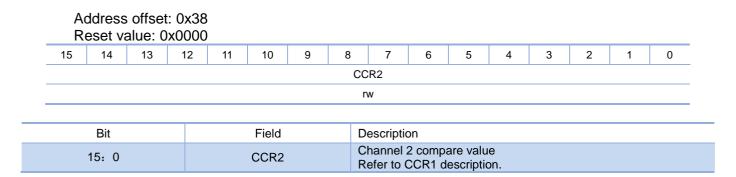

|    |      | 10.5.15            | TIM1_CCR2 Compare Register 2                                        |       |

|    |      | 10.5.17            | TIM1_CCR4 Compare Register 4                                        |       |

|    |      | 10.5.18            | TIM1_BDTR Break and Dead-Time Register                              |       |

|    |      | 10.5.19            | TIM1_DCR DMA Control Register                                       |       |

|    |      | 10.5.20            | TIM1_DMAR DMA Address Register of Continuous Mode                   |       |

|    |      | 10.5.21            | TIM1_CCMR3 Compare Mode Register 3                                  |       |

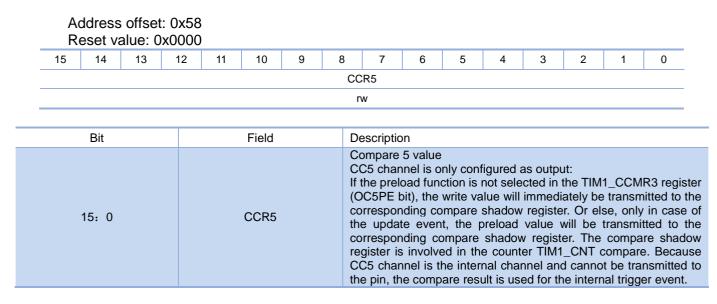

|    |      | 10.5.22            | TIM1_CCR5 Compare Register 5                                        |       |

|    |      | 10.5.23            | TIM1_PDER PWM Phase Shift/DMA Repeat Update Request Enable Register |       |

|    |      | 10.5.24            | TIM1_CCRxFALL PWM Phase Shift Count Down Compare Register           |       |

|    |      | 10.5.25            | TIM1_BKINF Break Input Filter Register                              |       |

| 11 |      |                    | eneral-Purpose Timer                                                |       |

| 11 | 11.1 |                    | Overview                                                            |       |

|    | 11.2 |                    | Function block diagram                                              |       |

|    | 11.3 |                    | Main characteristics                                                |       |

|    | 11.4 |                    | Function description                                                |       |

|    |      |                    | · · · · · · · · · · · · · · · · · · ·                               |       |

|    |                      | 11.4.1                                                                     | Clock                                                                                                                                                                                                                                                           |                                                                                                |

|----|----------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

|    |                      | 11.4.2                                                                     | Input capture                                                                                                                                                                                                                                                   |                                                                                                |

|    |                      | 11.4.3                                                                     | Output compare                                                                                                                                                                                                                                                  |                                                                                                |

|    |                      | 11.4.4                                                                     | Slave mode                                                                                                                                                                                                                                                      |                                                                                                |

|    |                      | 11.4.5                                                                     | Timer synchronization                                                                                                                                                                                                                                           |                                                                                                |

|    |                      | 11.4.6                                                                     | Timer XOR function                                                                                                                                                                                                                                              |                                                                                                |

|    |                      | 11.4.7                                                                     | Debug mode                                                                                                                                                                                                                                                      |                                                                                                |

|    |                      | 11.4.8                                                                     | Interrupt                                                                                                                                                                                                                                                       |                                                                                                |

|    |                      | 11.4.9                                                                     | DMA                                                                                                                                                                                                                                                             |                                                                                                |

|    | 11.5                 |                                                                            | Register                                                                                                                                                                                                                                                        |                                                                                                |

|    |                      | 11.5.1                                                                     | TIMx_CR1 Control Register 1                                                                                                                                                                                                                                     |                                                                                                |

|    |                      | 11.5.2                                                                     | TIMx_CR2 Control Register 2                                                                                                                                                                                                                                     |                                                                                                |

|    |                      | 11.5.3                                                                     | TIMx_SMCR Slave Mode Control Register                                                                                                                                                                                                                           |                                                                                                |

|    |                      | 11.5.4                                                                     | TIMx_DIER DMA/Interrupt Enable Register                                                                                                                                                                                                                         |                                                                                                |

|    |                      | 11.5.5                                                                     | TIMx_SR Status Register                                                                                                                                                                                                                                         |                                                                                                |

|    |                      | 11.5.6                                                                     | TIMx_EGR Event Generation Register                                                                                                                                                                                                                              |                                                                                                |

|    |                      | 11.5.7                                                                     | TIMx_CCMR1 Capture/Compare Mode Register 1                                                                                                                                                                                                                      |                                                                                                |

|    |                      | 11.5.8                                                                     | TIMx_CCMR2 Capture/Compare Mode Register 2                                                                                                                                                                                                                      |                                                                                                |

|    |                      | 11.5.9                                                                     | TIMx_CCER Capture/Compare Enable Register                                                                                                                                                                                                                       |                                                                                                |

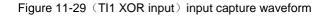

|    |                      | 11.5.10                                                                    | TIMx_COLIC Capitale/Compare Enable Register                                                                                                                                                                                                                     |                                                                                                |

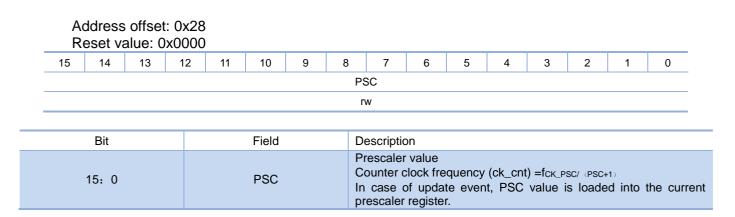

|    |                      | 11.5.11                                                                    | TIMx_PSC Prescaler                                                                                                                                                                                                                                              |                                                                                                |

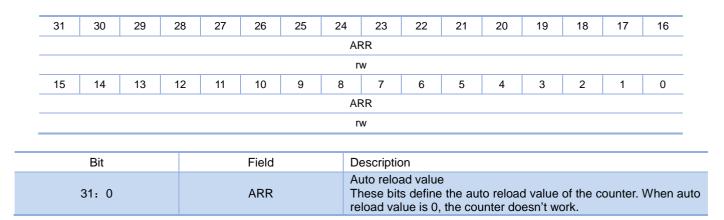

|    |                      | 11.5.12                                                                    | TIMX_R ARR Auto Reload Register                                                                                                                                                                                                                                 |                                                                                                |

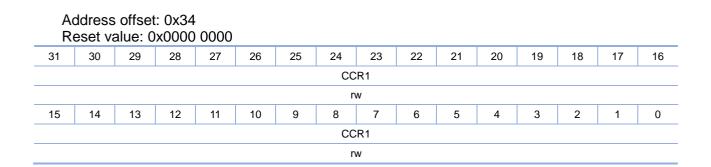

|    |                      | 11.5.12                                                                    | TIMx_CCR1 Capture/Compare Register 1                                                                                                                                                                                                                            |                                                                                                |

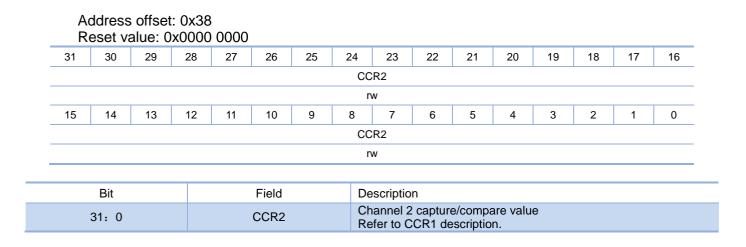

|    |                      | 11.5.14                                                                    | TIMx_CCR2 Capture/Compare Register 2                                                                                                                                                                                                                            |                                                                                                |

|    |                      | 11.5.14                                                                    |                                                                                                                                                                                                                                                                 |                                                                                                |

|    |                      |                                                                            | TIMx_CCR3 Capture/Compare Register 3                                                                                                                                                                                                                            |                                                                                                |

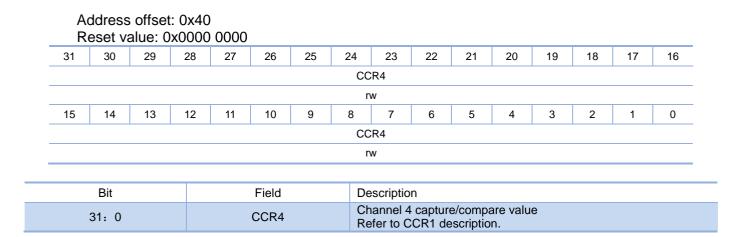

|    |                      | 11.5.16                                                                    | TIMx_CCR4 Capture/Compare Register 4                                                                                                                                                                                                                            |                                                                                                |

|    |                      | 11.5.17                                                                    | TIMx_DCR DMA Control Register                                                                                                                                                                                                                                   |                                                                                                |

|    |                      | 11.5.18                                                                    | TIMx_DMAR DMA Address Register of Continuous Mode                                                                                                                                                                                                               |                                                                                                |

|    |                      | 11.5.19                                                                    | TIMx_OR Input Option Register                                                                                                                                                                                                                                   |                                                                                                |

| 12 |                      | TIM6 Ba                                                                    | asic Timer                                                                                                                                                                                                                                                      | 174                                                                                            |

|    | 12.1                 |                                                                            | Overview                                                                                                                                                                                                                                                        |                                                                                                |

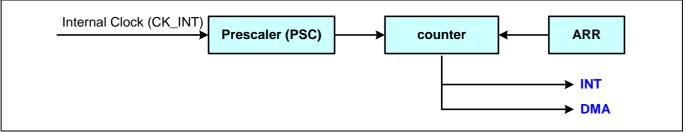

|    | 12.2                 |                                                                            | Function block diagram                                                                                                                                                                                                                                          |                                                                                                |

|    | 12.3                 |                                                                            | Main characteristics                                                                                                                                                                                                                                            |                                                                                                |

|    | 12.4                 |                                                                            | Function description                                                                                                                                                                                                                                            |                                                                                                |

|    |                      | 12.4.1                                                                     | Clock                                                                                                                                                                                                                                                           |                                                                                                |

|    |                      | 12.4.2                                                                     | Debug mode                                                                                                                                                                                                                                                      |                                                                                                |

|    |                      | 12.4.3                                                                     | Interrupt                                                                                                                                                                                                                                                       |                                                                                                |

|    |                      | 12.4.4                                                                     | DMA                                                                                                                                                                                                                                                             |                                                                                                |

|    | 12.5                 |                                                                            | Register                                                                                                                                                                                                                                                        |                                                                                                |

|    |                      | 12.5.1                                                                     | TIMx_CR1 Control Register 1                                                                                                                                                                                                                                     |                                                                                                |

|    |                      | 12.5.2                                                                     |                                                                                                                                                                                                                                                                 |                                                                                                |

|    |                      | 12.0.2                                                                     | TIMx_DIER DMA/Interrupt Enable Register                                                                                                                                                                                                                         |                                                                                                |

|    |                      | 12.5.2                                                                     | TIMx_DIER DMA/Interrupt Enable Register<br>TIMx_SR Status Register                                                                                                                                                                                              |                                                                                                |

|    |                      |                                                                            | TIMx_SR Status Register                                                                                                                                                                                                                                         |                                                                                                |

|    |                      | 12.5.3                                                                     | TIMx_SR Status Register<br>TIMx_EGR Event Generation Register                                                                                                                                                                                                   |                                                                                                |

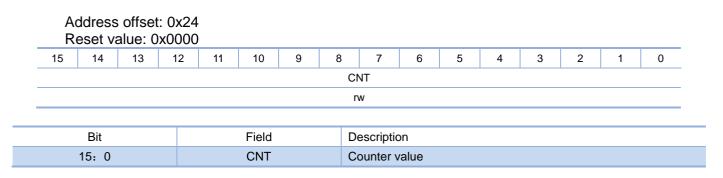

|    |                      | 12.5.3<br>12.5.4                                                           | TIMx_SR Status Register<br>TIMx_EGR Event Generation Register<br>TIMx_CNT Counter                                                                                                                                                                               |                                                                                                |

|    |                      | 12.5.3<br>12.5.4<br>12.5.5                                                 | TIMx_SR Status Register<br>TIMx_EGR Event Generation Register<br>TIMx_CNT Counter<br>TIMx_PSC Prescaler                                                                                                                                                         |                                                                                                |

| 13 |                      | 12.5.3<br>12.5.4<br>12.5.5<br>12.5.6<br>12.5.7                             | TIMx_SR Status Register<br>TIMx_EGR Event Generation Register<br>TIMx_CNT Counter<br>TIMx_PSC Prescaler<br>TIMx_ARR Auto Reload Register                                                                                                                        |                                                                                                |

| 13 |                      | 12.5.3<br>12.5.4<br>12.5.5<br>12.5.6<br>12.5.7                             | TIMx_SR Status Register<br>TIMx_EGR Event Generation Register<br>TIMx_CNT Counter<br>TIMx_PSC Prescaler<br>TIMx_ARR Auto Reload Register<br><b>4 Basic Timer</b>                                                                                                |                                                                                                |

| 13 | 13.1                 | 12.5.3<br>12.5.4<br>12.5.5<br>12.5.6<br>12.5.7                             | TIMx_SR Status Register<br>TIMx_EGR Event Generation Register<br>TIMx_CNT Counter<br>TIMx_PSC Prescaler<br>TIMx_ARR Auto Reload Register<br><b>4 Basic Timer</b><br>Overview                                                                                    |                                                                                                |

| 13 | 13.1<br>13.2         | 12.5.3<br>12.5.4<br>12.5.5<br>12.5.6<br>12.5.7                             | TIMx_SR Status Register<br>TIMx_EGR Event Generation Register<br>TIMx_CNT Counter<br>TIMx_PSC Prescaler<br>TIMx_ARR Auto Reload Register<br><b>4 Basic Timer</b><br>Overview<br>Function block diagram                                                          | 178<br>178<br>178<br>178<br>178<br>179<br>179<br><b>180</b><br>180<br>180                      |

| 13 | 13.1<br>13.2<br>13.3 | 12.5.3<br>12.5.4<br>12.5.5<br>12.5.6<br>12.5.7                             | TIMx_SR Status Register<br>TIMx_EGR Event Generation Register<br>TIMx_CNT Counter<br>TIMx_PSC Prescaler<br>TIMx_ARR Auto Reload Register<br><b>4 Basic Timer</b><br>Overview<br>Function block diagram<br>Main characteristics                                  | 178<br>178<br>178<br>178<br>178<br>179<br><b>180</b><br>180<br>180<br>180                      |

| 13 | 13.1<br>13.2         | 12.5.3<br>12.5.4<br>12.5.5<br>12.5.6<br>12.5.7<br>TIM13/1                  | TIMx_SR Status Register                                                                                                                                                                                                                                         | 178<br>178<br>178<br>178<br>178<br>178<br>179<br><b>180</b><br>180<br>180<br>180<br>180<br>181 |

| 13 | 13.1<br>13.2<br>13.3 | 12.5.3<br>12.5.4<br>12.5.5<br>12.5.6<br>12.5.7<br><b>TIM13/1</b><br>13.4.1 | TIMx_SR Status Register<br>TIMx_EGR Event Generation Register<br>TIMx_CNT Counter<br>TIMx_PSC Prescaler<br>TIMx_ARR Auto Reload Register<br><b>4 Basic Timer</b><br>Overview<br>Function block diagram<br>Main characteristics<br>Function description<br>Clock | 178<br>178<br>178<br>178<br>178<br>179<br><b>180</b><br>180<br>180<br>180<br>180<br>181        |

| 13 | 13.1<br>13.2<br>13.3 | 12.5.3<br>12.5.4<br>12.5.5<br>12.5.6<br>12.5.7<br>TIM13/1                  | TIMx_SR Status Register                                                                                                                                                                                                                                         | 178<br>178<br>178<br>178<br>178<br>179<br><b>180</b><br>180<br>180<br>180<br>180<br>181<br>181 |

|    |      | 13.4.4           | Debug mode                                              |     |

|----|------|------------------|---------------------------------------------------------|-----|

|    |      | 13.4.5           | Interrupt                                               |     |

|    |      | 13.4.6           | DMA                                                     |     |

|    | 13.5 |                  | Register                                                |     |

|    |      | 13.5.1           | TIMx_CR1 Control Register 1                             |     |

|    |      | 13.5.2           | TIMx_DIER DMA/Interrupt Enable Register                 |     |

|    |      | 13.5.3           | TIMx_SR Status Register                                 |     |

|    |      | 13.5.4           | TIMx_EGR Event Generation Register                      |     |

|    |      | 13.5.5           | TIMx_CCMR1 Capture/Compare Mode Register 1              |     |

|    |      | 13.5.6           | TIMx_CCER Capture/Compare Enable Register               |     |

|    |      | 13.5.7           | TIMx_CNT Counter                                        |     |

|    |      | 13.5.8           | TIMx PSC Prescaler                                      |     |

|    |      | 13.5.9           | TIMx_ARR Auto Reload Register                           |     |

|    |      | 13.5.10          | TIMx_CCR1 Capture/Compare Register 1                    |     |

|    |      | 13.5.11          | TIMx_BDTR Break and Dead-Time Register                  |     |

| 14 |      |                  | ndependent watchdog                                     |     |

| 14 | 14.1 |                  | Introduction                                            |     |

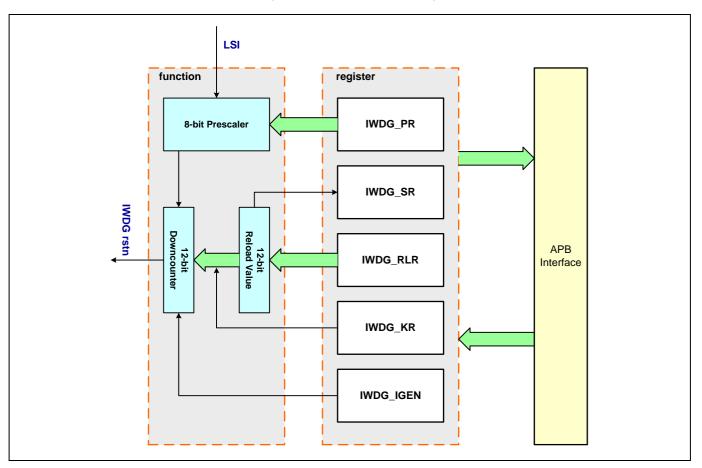

|    | 14.1 |                  | Functional block diagram                                |     |

|    | 14.2 |                  | Main features                                           |     |

|    | 14.3 |                  |                                                         |     |

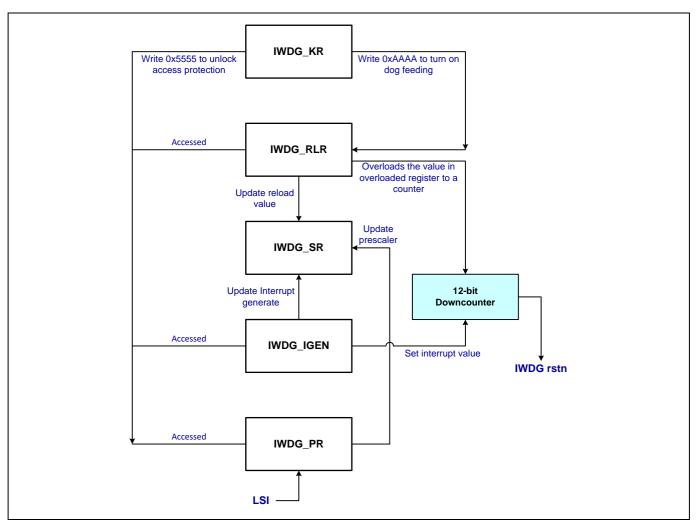

|    | 14.4 |                  | Functional description                                  |     |

|    |      | 14.4.1<br>14.4.2 | Flow block diagram                                      |     |

|    |      |                  | Independent watchdog timeout                            |     |

|    | 445  | 14.4.3           | Interrupt                                               |     |

|    | 14.5 | 4454             | Register                                                |     |

|    |      | 14.5.1           | Overview of registers                                   |     |

|    |      | 14.5.2           | IWDG_KR Key Register                                    |     |

|    |      | 14.5.3           | IWDG_PR Prescaler Register                              |     |

|    |      | 14.5.4           | IWDG_RLR Reload Register                                |     |

|    |      | 14.5.5           | IWDG_SR Status Register                                 |     |

|    |      | 14.5.6           | IWDG_CR Control Register                                |     |

|    |      | 14.5.7           | IWDG_IGEN Interrupt Generate Register                   |     |

|    |      | 14.5.8           | IWDG_CNT Counter Register                               | 200 |

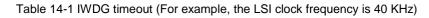

| 15 |      | USART            | Universal Synchronous Asynchronous Receiver Transmitter |     |

|    | 15.1 |                  | Introduction                                            |     |

|    | 15.2 |                  | USART features                                          |     |

|    | 15.3 |                  | USART functional description                            |     |

|    |      | 15.3.1           | Functional block diagram                                |     |

|    |      | 15.3.2           | Signal description                                      |     |

|    |      | 15.3.3           | Functional description                                  |     |

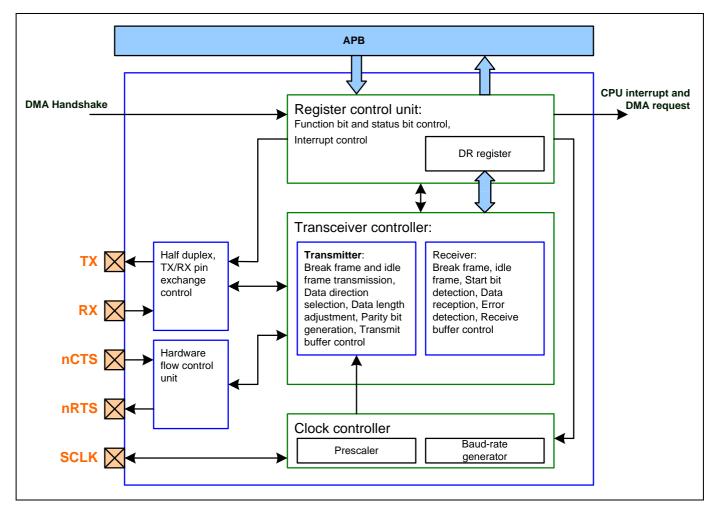

|    |      | 15.3.4           | Character description                                   |     |

|    |      | 15.3.5           | Baud rate generator                                     |     |

|    |      | 15.3.6           | Sampling                                                |     |

|    |      | 15.3.7           | Parity check control                                    |     |

|    |      | 15.3.8           | Transmitter                                             |     |

|    |      | 15.3.9           | Receiver                                                |     |

|    |      | 15.3.10          | Synchronous mode                                        |     |

|    |      | 15.3.11          | Single-wire half-duplex communication                   |     |

|    |      | 15.3.12          | Hardware flow control                                   |     |

|    |      | 15.3.13          | Interrupts                                              |     |

|    |      | 15.3.14          | DMA                                                     |     |

|    | 15.4 |                  | Register                                                |     |

|    |      | 15.4.1           | Overview of registers                                   |     |

|    |      | 15.4.2           | USART_SR status register                                |     |

|    |      | 15.4.3           | USART_DR data register                                  | 210 |

|    |      | 15.4.4             | USART_BRR baud rate register                                                         | 211 |

|----|------|--------------------|--------------------------------------------------------------------------------------|-----|

|    |      | 15.4.5             | USART_CR1 control register 1                                                         |     |

|    |      | 15.4.6             | USART_CR2 control register 2                                                         | 213 |

|    |      | 15.4.7             | USART_CR3 control register 3                                                         | 213 |

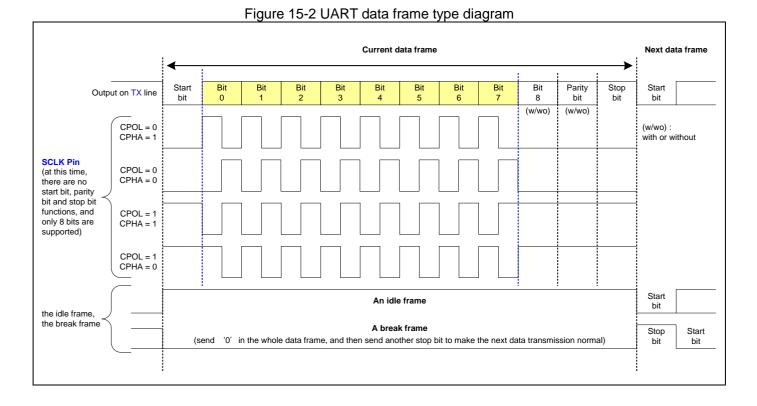

| 16 |      | ADC An             | alog-to-digital converter                                                            |     |

|    | 16.1 |                    | Introduction                                                                         |     |

|    | 16.2 |                    | Functional block diagram                                                             |     |

|    | 17.1 |                    | Main features                                                                        |     |

|    | 17.2 |                    | Interrupt                                                                            |     |

|    | 17.3 |                    | DMA                                                                                  |     |

|    | 17.4 |                    | Functional description                                                               |     |

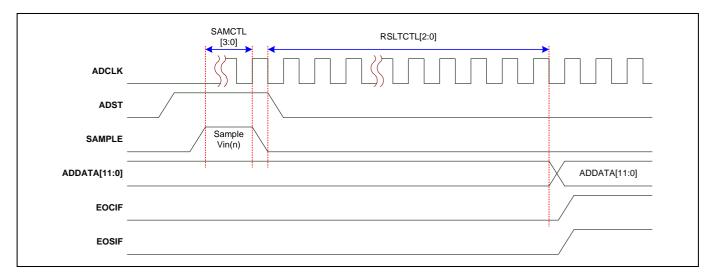

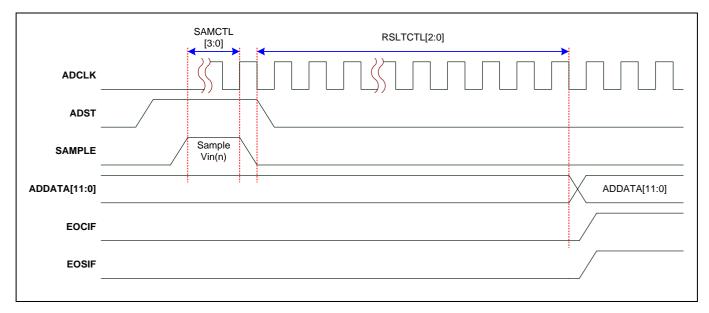

|    |      | 17.4.1             | Clock                                                                                | 217 |

|    |      | 17.4.2             | Data offset                                                                          | 217 |

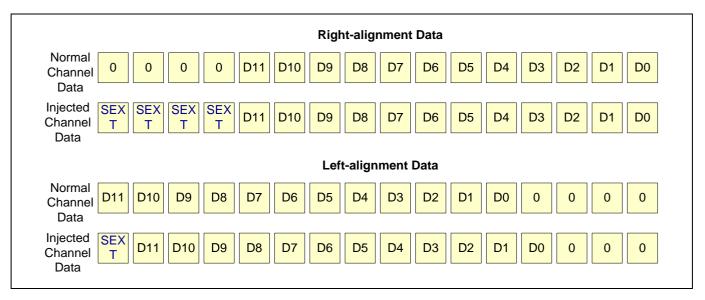

|    |      | 17.4.3             | Data alignment                                                                       | 217 |

|    |      | 17.4.4             | Programmable resolution                                                              | 218 |

|    |      | 17.4.5             | Programmable sampling time                                                           | 218 |

|    |      | 17.4.6             | Data channel register                                                                | 218 |

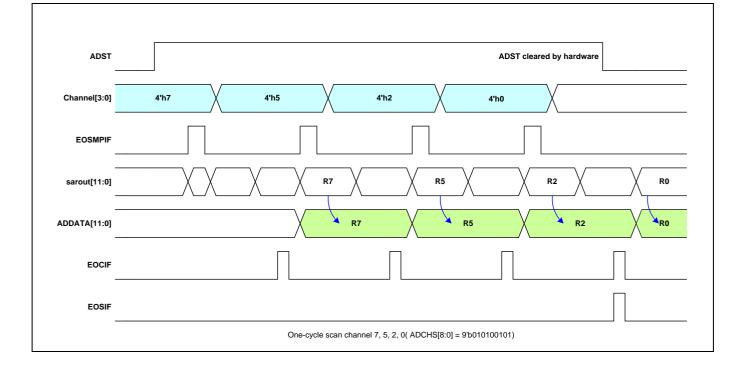

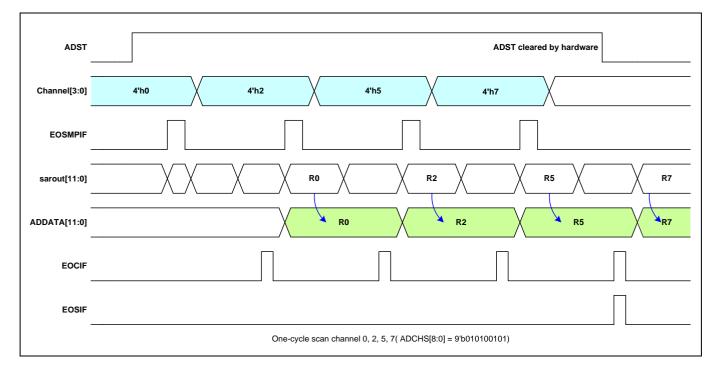

|    |      | 17.4.7             | Channel selection                                                                    | 219 |

|    | 17.5 |                    | ADC on-off control                                                                   | 219 |

|    |      | 17.5.1             | Normal channel conversion                                                            |     |

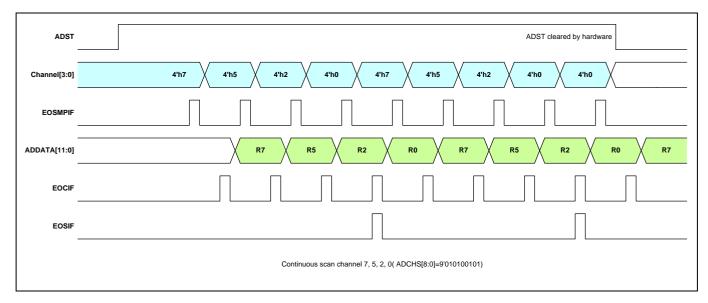

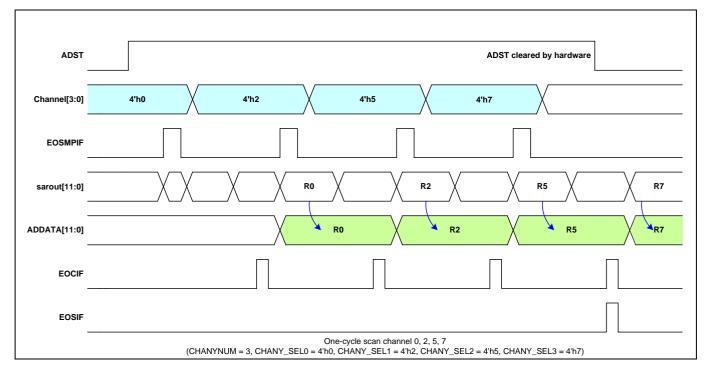

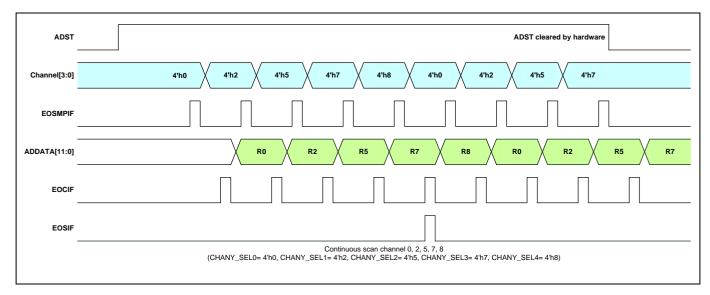

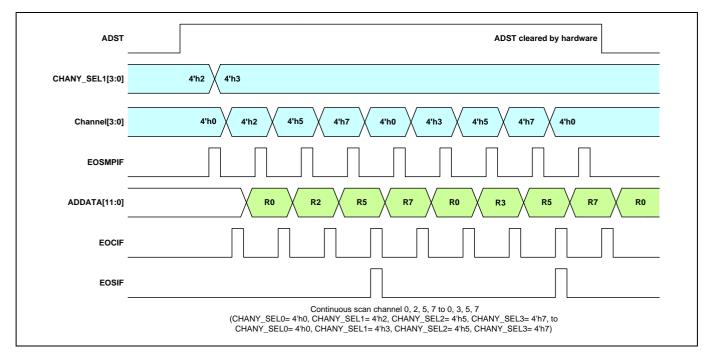

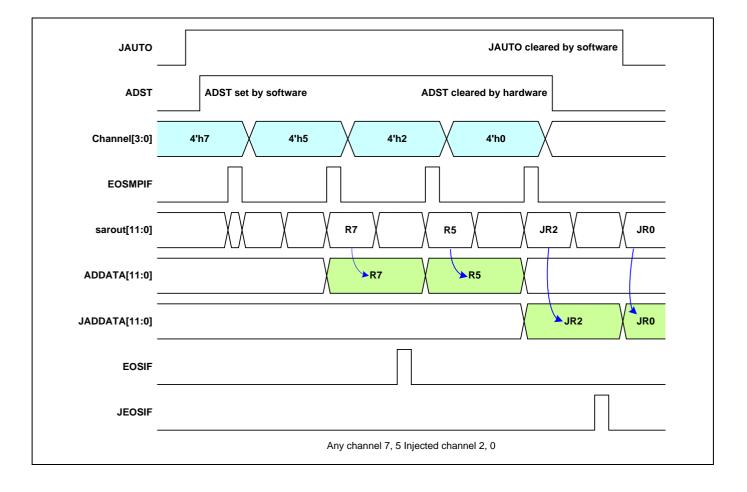

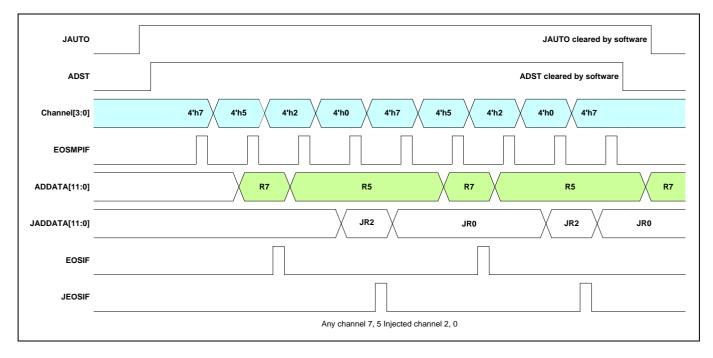

|    |      | 17.5.2             | Any channel conversion                                                               |     |

|    |      | 17.5.3             | Injected channel conversion                                                          |     |

|    |      | 17.5.4             | ADC trigger signal                                                                   |     |

|    |      | 17.5.5             | Analog watchdog                                                                      |     |

|    |      | 17.5.6             | Internal temperature sensor                                                          |     |

|    |      | 17.5.7             | Internal voltage sensor                                                              |     |

|    | 17.6 |                    | Register description                                                                 |     |

|    |      | 17.6.1             | Overview of registers                                                                |     |

|    |      | 17.6.2             | ADC_ADDATA Data Register                                                             |     |

|    |      | 17.6.3             | ADC_ADCFG Configuration Register                                                     |     |

|    |      | 17.6.4             | ADC_ADCR Control Register                                                            |     |

|    |      | 17.6.5             | ADC_ADCHS Channel Selection Register                                                 |     |

|    |      | 17.6.6             | ADC_ADCMPR Analog Watchdog Compare Register                                          |     |

|    |      | 17.6.7             | ADC_ADSTA Status Register                                                            |     |

|    |      | 17.6.8             | ADC_ADDRn Channel Data Register (n=0~10)                                             |     |

|    |      | 17.6.9             | ADC_ADSTA_EXT Extended State Register                                                |     |

|    |      | 17.6.10<br>17.6.11 | ADC_CHANY0 Any Channel Selection Register 0                                          |     |

|    |      | 17.6.12            | ADC_CHANY1 Any Channel Selection Register 1                                          |     |

|    |      | 17.6.12            | ADC_ANY_CFG Any Channel Configuration Register                                       |     |

|    |      | 17.6.13            | ADC_ANY_CR Any Channel Control Register<br>ADC_SMPR1 Sample Configuration Register 1 |     |

|    |      | 17.6.15            | ADC_SMPR2 Sample Configuration Register 2                                            |     |

|    |      | 17.6.16            | ADC_JOFRn Injected Channel Data Offset Register (n=0~3)                              |     |

|    |      | 17.6.17            | ADC_JSQR Injected Sequence Register                                                  |     |

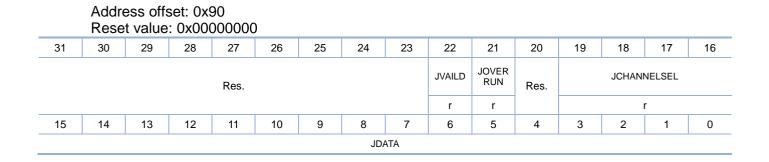

|    |      | 17.6.18            | ADC_JADDATA Injected Data Register                                                   |     |

|    |      | 17.6.19            | ADC_JDRn Injected Channel Data Register (n=0~3)                                      |     |

|    |      | 17.6.20            | ADC_DDATA Last Conversion Data Register                                              |     |

|    |      | 17.6.21            | ADC_LDATA Last conversion Data Register                                              |     |

| 40 |      |                    |                                                                                      |     |

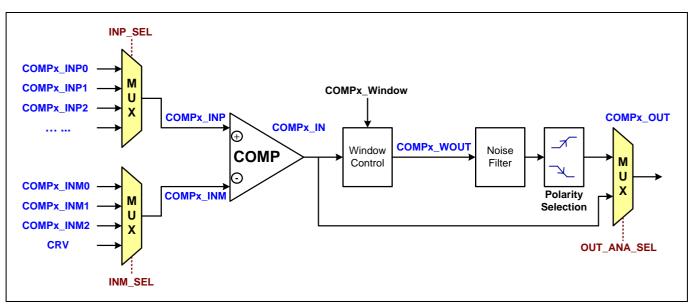

| 18 |      | COMPO              | Comparator                                                                           |     |

|    | 18.1 |                    | Overview                                                                             |     |

|    | 18.2 |                    | Functional block diagram                                                             |     |

|    | 18.3 |                    | Main characteristics                                                                 |     |

|    | 18.4 | 10 / 4             | Functional description                                                               |     |

|    |      | 18.4.1             | COMP clocks and reset                                                                |     |

|    |      | 18.4.2 | COMP switch                                           |     |

|----|------|--------|-------------------------------------------------------|-----|

|    |      | 18.4.3 | COMP inputs and outputs                               | 247 |

|    |      | 18.4.4 | COMP channel selection                                | 247 |

|    |      | 18.4.5 | Interrupt and wakeup                                  | 248 |

|    |      | 18.4.6 | Power mode                                            |     |

|    |      | 18.4.7 | Comparator LOCK mechanism                             | 248 |

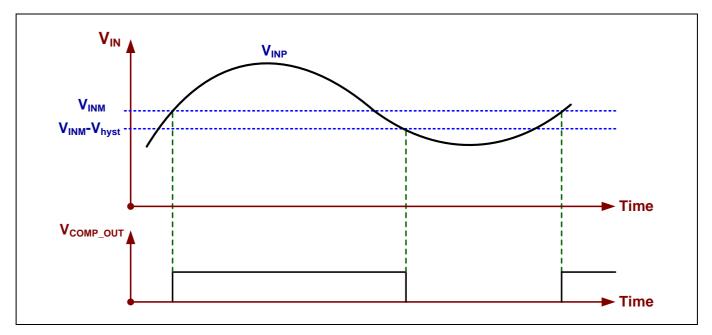

|    |      | 18.4.8 | Hysteresis voltage                                    |     |

|    | 18.5 |        | Register                                              | 249 |

|    |      | 18.5.1 | COMPx_CSR (COMP control and status register) (x=1, 2) | 249 |

|    |      | 18.5.2 | COMP_CRV (COMP external reference voltage register)   |     |

|    |      | 18.5.3 | COMPx_POLL (COMP polling register) (x=1, 2)           | 251 |

| 19 |      | OPAME  | Operational Amplifier1/2                              | 253 |

| 10 | 19.1 |        | Overview                                              |     |

|    | 19.2 |        | Main characteristics                                  |     |

|    | 19.3 |        | Functional description                                |     |

|    | 10.0 | 19.3.1 | Clock                                                 |     |

|    | 19.4 |        | Register                                              |     |

|    | 13.4 | 19.4.1 | Overview of registers                                 |     |

|    |      | 19.4.2 | OPAMP_CR Configuration register                       |     |

|    |      |        |                                                       |     |

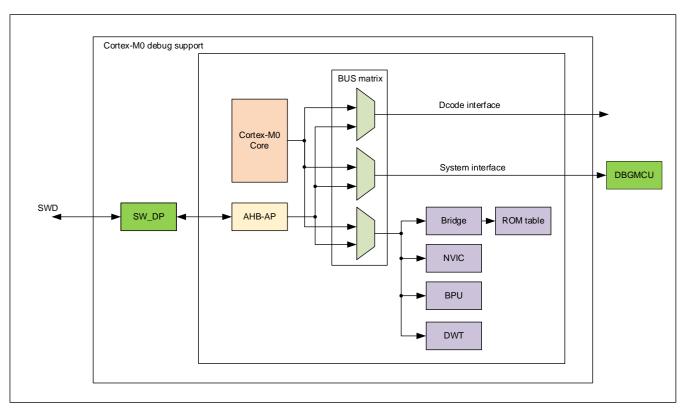

| 20 |      | DBG De | ebug Support                                          |     |

|    | 20.1 |        | Introduction                                          |     |

|    | 20.2 |        | Function descriptions                                 |     |

|    |      | 20.2.1 | Function block diagram                                |     |

|    |      | 20.2.2 | SWD internal pull up and down                         |     |

|    |      | 20.2.3 | SWJ debug port                                        |     |

|    | 20.3 |        | ID code and lock mechanism                            |     |

|    |      | 20.3.1 | Microcontroller device ID code                        |     |

|    |      | 20.3.2 | Cortex JEDEC-106 ID code                              |     |

|    | 20.4 |        | SW debug port                                         |     |

|    |      | 20.4.1 | SW protocol introduction                              |     |

|    |      | 20.4.2 | SW protocol series                                    |     |

|    |      | 20.4.3 | SW-DP status unit (Reset, Idle states, ID code)       |     |

|    |      | 20.4.4 | DP and AP read/write access                           |     |

|    |      | 20.4.5 | SW-DP register                                        |     |

|    |      | 20.4.6 | SW-AP register                                        |     |

|    | 20.5 |        | MCU debug module (DBGMCU)                             |     |

|    |      | 20.5.1 | Debug support at low power mode                       |     |

|    |      | 20.5.2 | Support timer, watchdog                               |     |

|    | 20.6 |        | Register                                              |     |

|    |      | 20.6.1 | Register overview                                     |     |

|    |      | 20.6.2 | DBG_IDCODE ID Encode Register                         |     |

|    |      | 20.6.3 | DBG_CR Control Register                               |     |

| 21 |      | Device | Electronic Signature                                  |     |

|    | 21.1 |        | Overview                                              |     |

|    | 21.2 |        | Register description                                  |     |

|    |      | 21.2.1 | UID1 Unique Identifier                                |     |

|    |      | 21.2.2 | UID2 Unique Identifier                                |     |

|    |      | 21.2.3 | UID3 Unique Identifier                                |     |

| 22 |      |        | Records                                               |     |

| ۷۷ |      | matory | NGVVIU3                                               |     |

## Figures

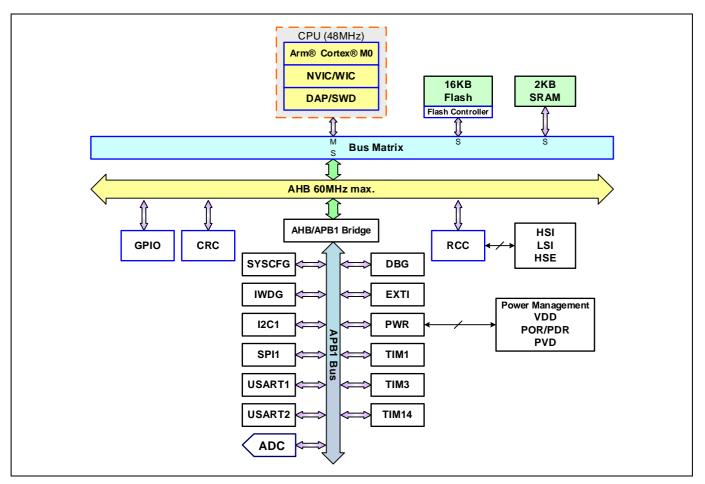

| Figure 1-1 System architecture block diagram                                           | 17  |

|----------------------------------------------------------------------------------------|-----|

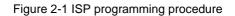

| Figure 2-1 ISP programming procedure                                                   | 25  |

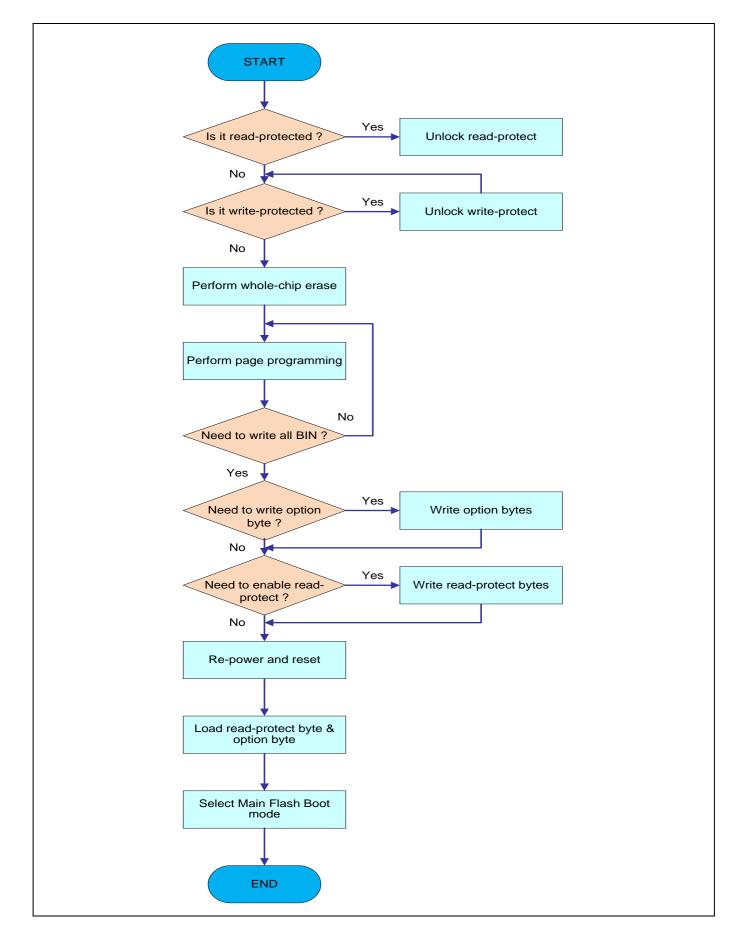

| Figure 2-2 IAP programming procedure                                                   | 26  |

| Figure 3-1 Power control block diagram                                                 | 40  |

| Figure 3-2 Power-on reset and power-down reset waveform                                | 42  |

| Figure 3-3 PVD threshold waveform                                                      | 42  |

| Figure 4-1 Reset functional block diagram                                              | 48  |

| Figure 4-2 Clock tree                                                                  |     |

| Figure 7-1 EXTI structure block diagram                                                |     |

| Figure 8-1 DMA functional block diagram                                                |     |

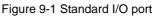

| Figure 9-1 Standard I/O port                                                           |     |

| Figure 9-2 Floating/pull-up/pull-down input configuration                              |     |

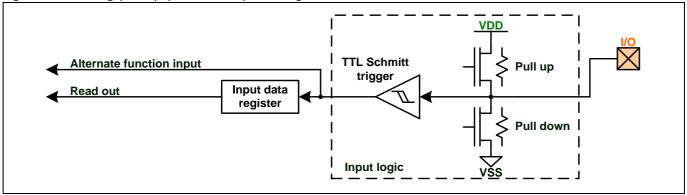

| Figure 9-3 Output configuration                                                        |     |

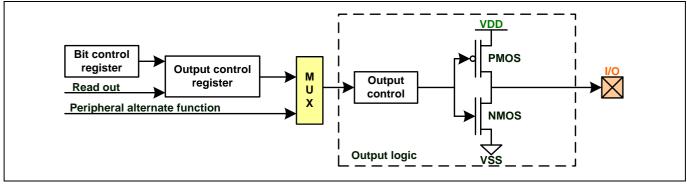

| Figure 9-4 Alternate function configuration                                            |     |

| Figure 9-5 Analog input                                                                |     |

| Figure 10-1 TIM1 block diagram                                                         |     |

| Figure 10-2 Clock selection                                                            |     |

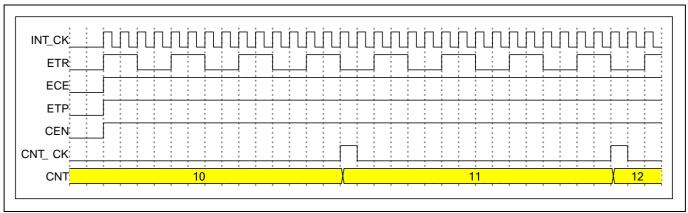

| Figure 10-3 Control circuit in external clock mode 1                                   |     |

| Figure 10-4 Control circuit in external clock mode 2                                   |     |

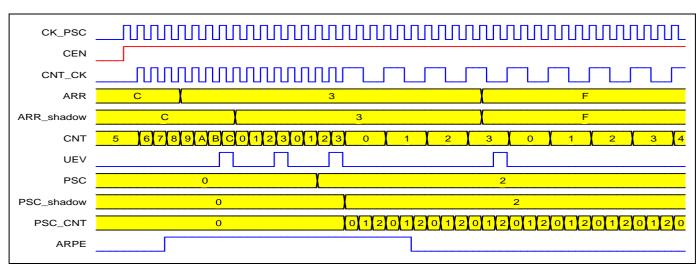

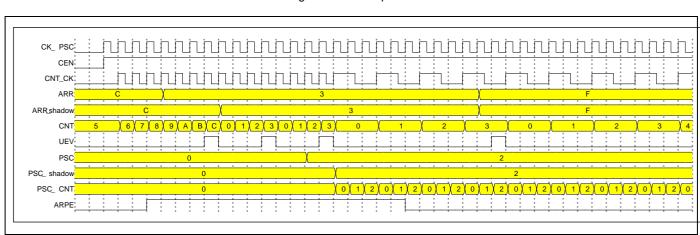

| Figure 10-5 Auto preload                                                               |     |

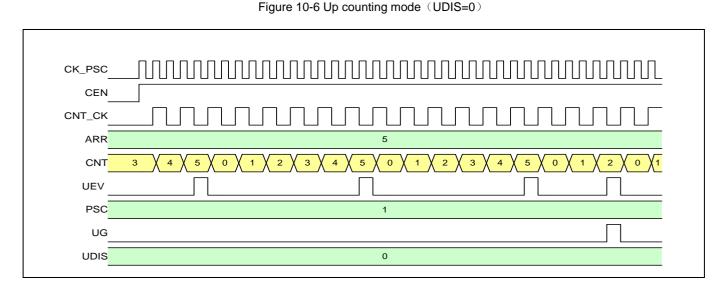

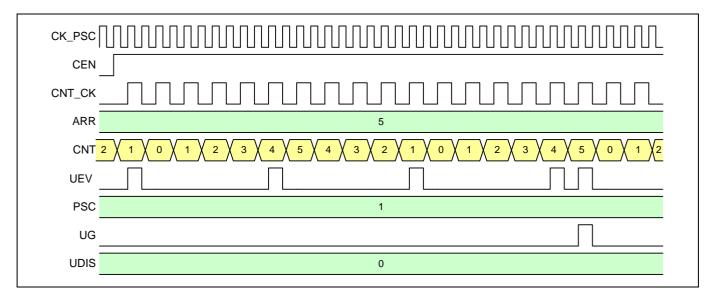

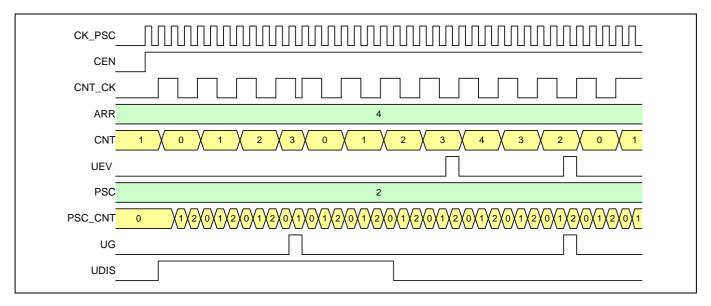

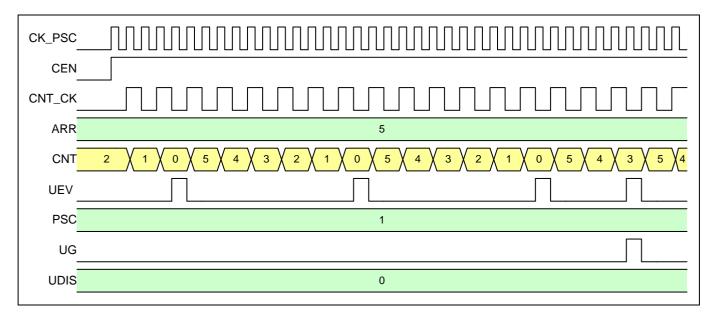

| Figure 10-6 Up counting mode (UDIS=0)                                                  |     |

| Figure 10-7 Up counting mode (UDIS=1, disable update event)                            |     |

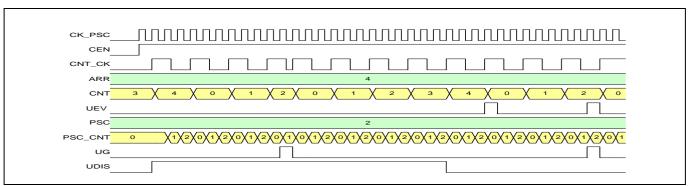

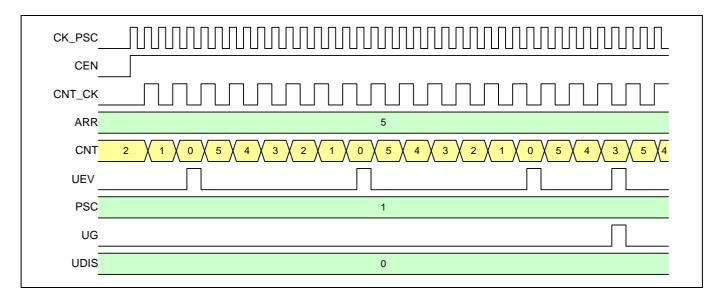

| Figure 10-8 Down counting mode (UDIS=0)                                                |     |

|                                                                                        |     |

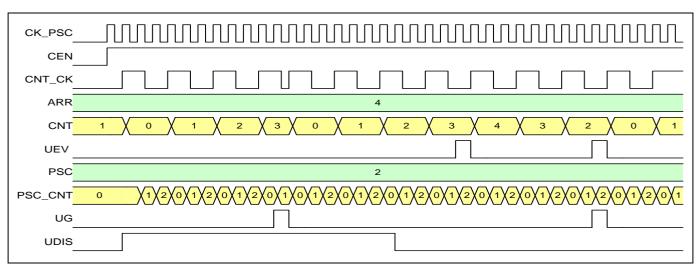

| Figure 10-9 Down counting mode (UDIS=1 disables update event)                          |     |

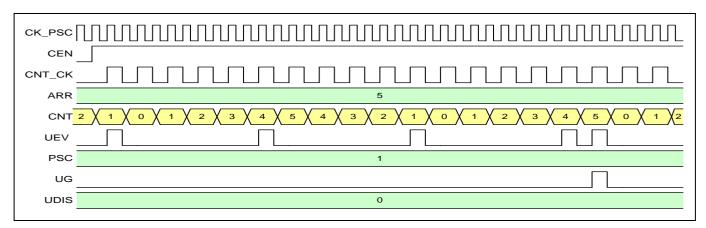

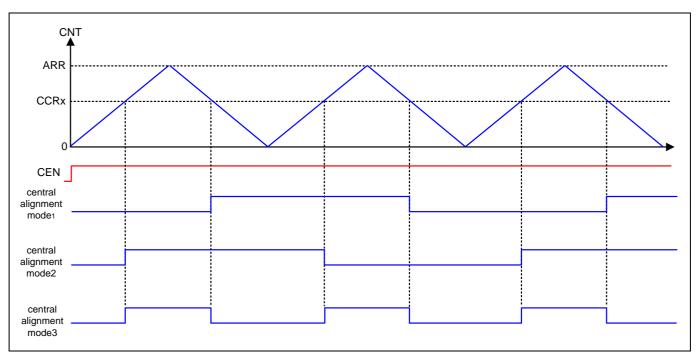

| Figure 10-10 Central count mode (UDIS=0)                                               |     |

| Figure 10-11 Central count mode (UDIS=1 disables update event)                         |     |

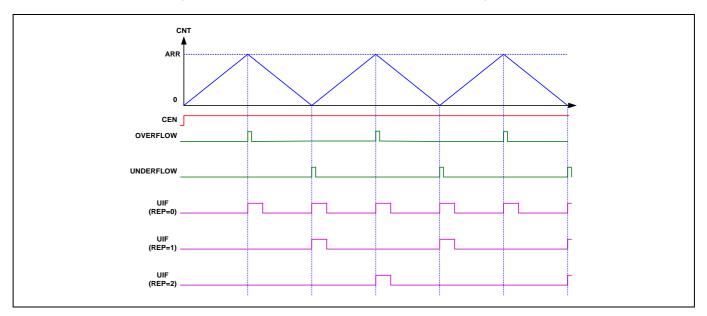

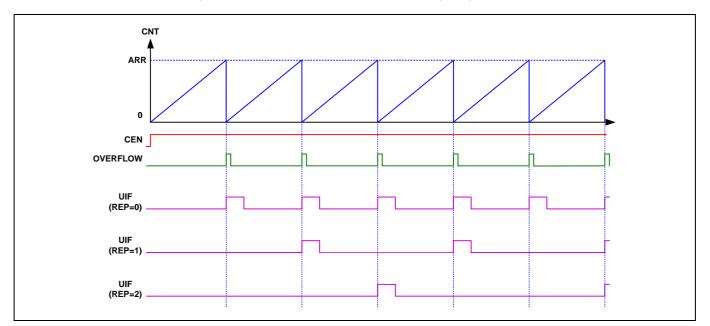

| Figure 10-12 Repeat count time sequence in the central alignment mode                  |     |

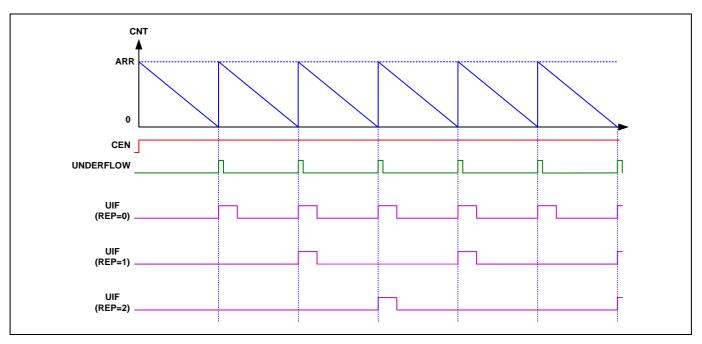

| Figure 10-13 Up count time sequence in the edge alignment mode                         |     |

| Figure 10-14 Down count time sequence in the edge alignment mode                       |     |

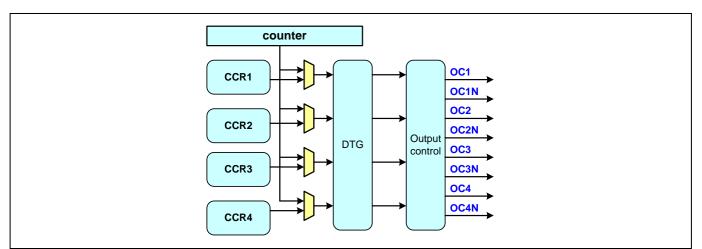

| Figure 10-15 Output compare block diagram                                              |     |

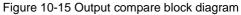

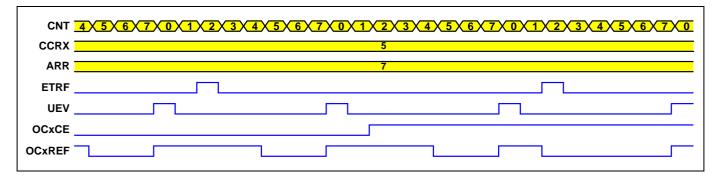

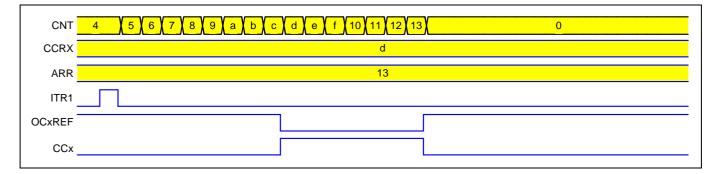

| Figure 10-16 Output compare mode, OC1 signals toggle when match                        |     |

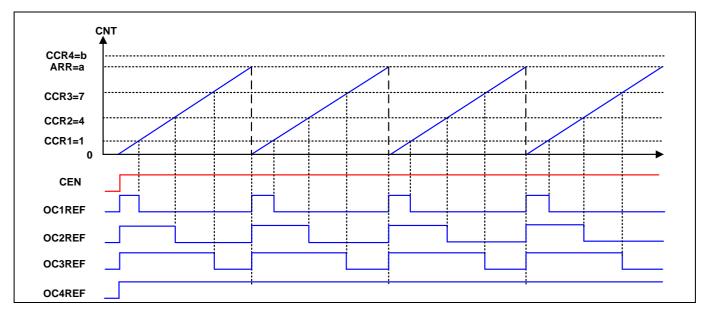

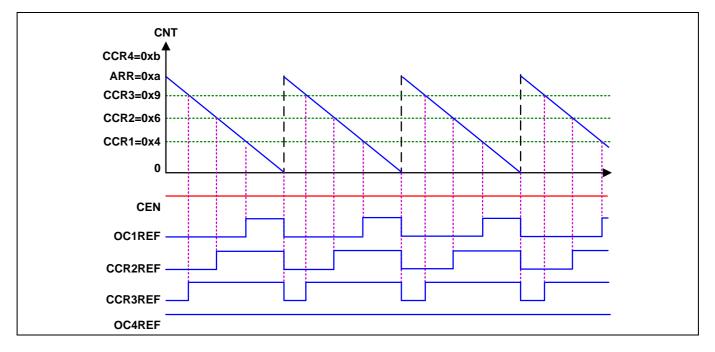

| Figure 10-17 Waveform in PWM mode 1 during edge alignment up count                     |     |

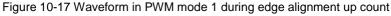

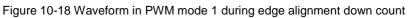

| Figure 10-18 Waveform in PWM mode 1 during edge alignment down count                   |     |

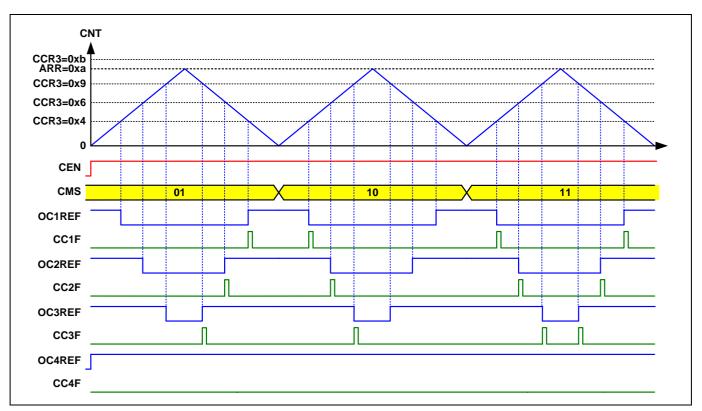

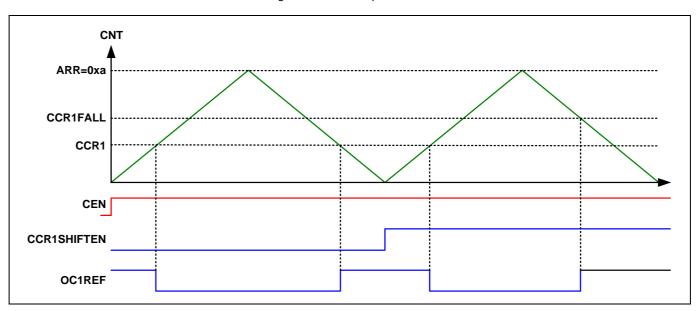

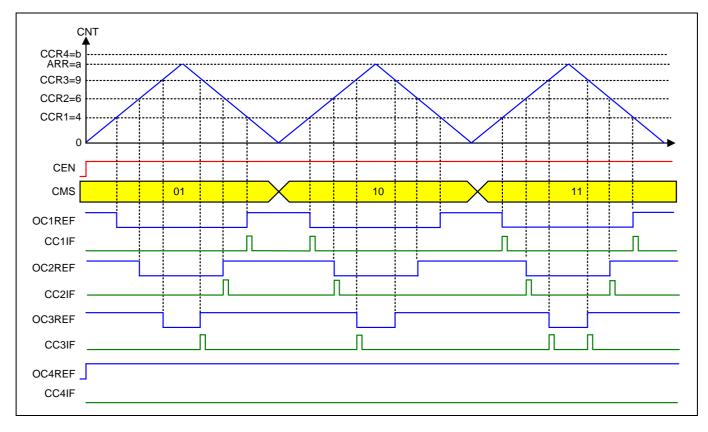

| Figure 10-19 Waveform in central alignment PWM mode 1                                  |     |

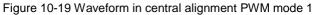

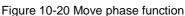

| Figure 10-20 Move phase function                                                       |     |

| Figure 10-21 Example of six step PWM with COM (OSSR = 1)                               |     |

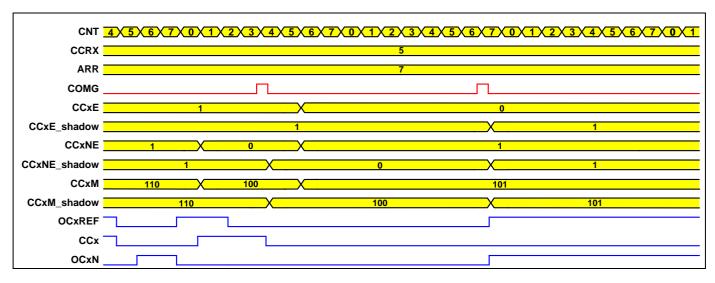

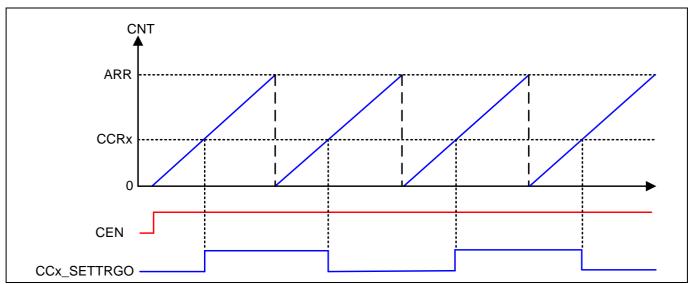

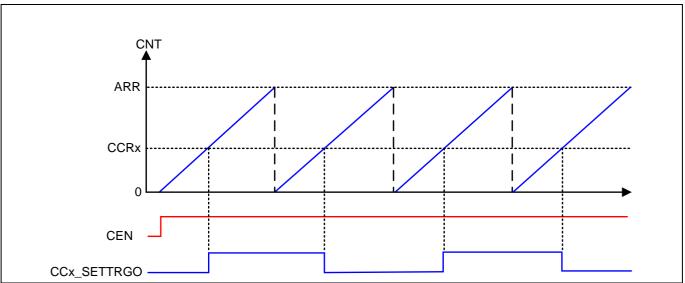

| Figure 10-22 CCx_SETTRGO in edge aligned incremental counting mode output example      |     |

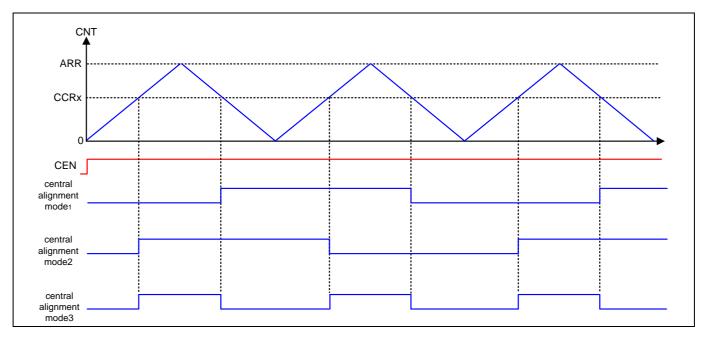

| Figure 10-23 CCx_SETTRGO in central aligned incremental counting mode output example   |     |

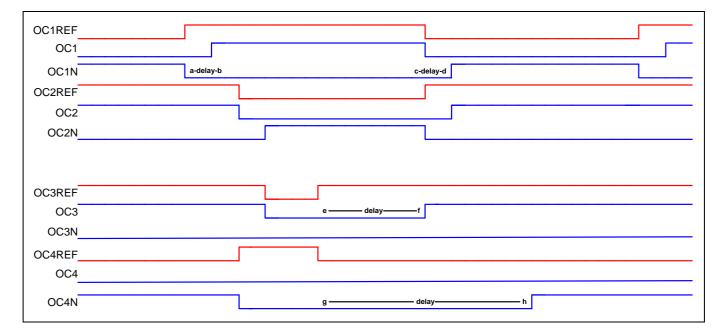

| Figure 10-24 Dead-time insertion                                                       |     |

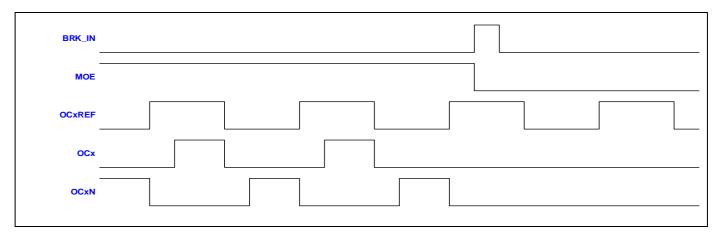

| Figure 10-25 Response break output (OISx=0, OISxN=0)                                   |     |

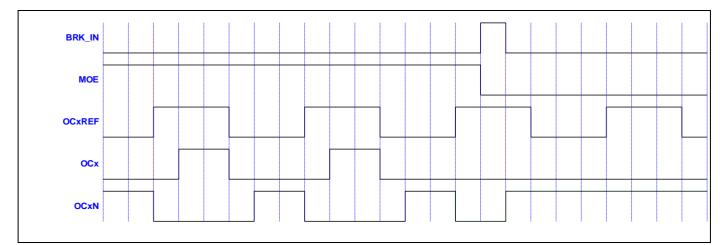

| Figure 10-26 Response break output (OISx=0, OISxN=1)                                   | 111 |

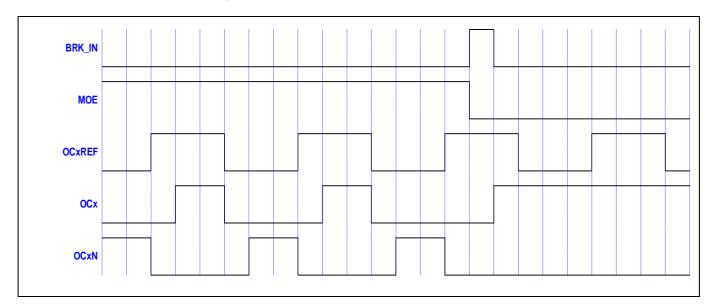

| Figure 10-27 Response break output (OISx=1,OISxN=0)                                    | 111 |

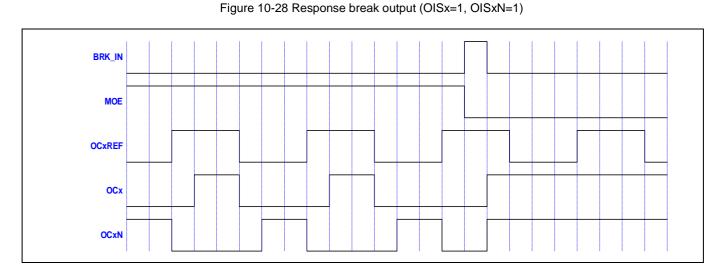

| Figure 10-28 Response break output (OISx=1, OISxN=1)                                   | 112 |

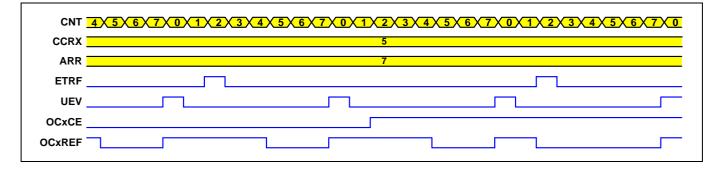

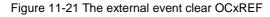

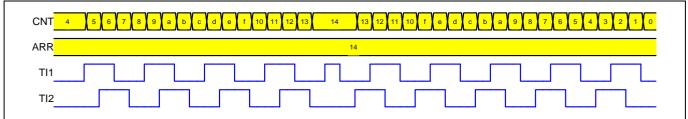

| Figure 10-29 The external event clear OCxREF                                           | 112 |

| Figure 10-30 one-pulse mode                                                            | 113 |

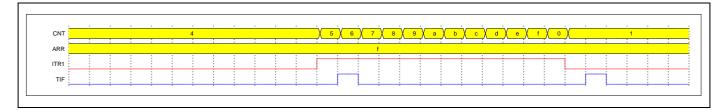

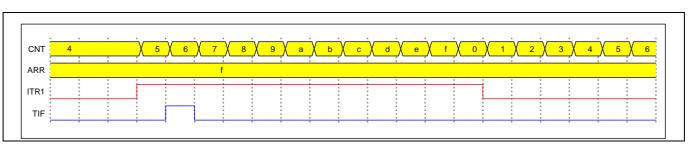

| Figure 10-31 Control time sequence in reset mode                                       | 114 |

| Figure 10-32 Control time sequence in gate mode                                        |     |

| Figure 10-33 Control time sequence in trigger mode                                     | 114 |

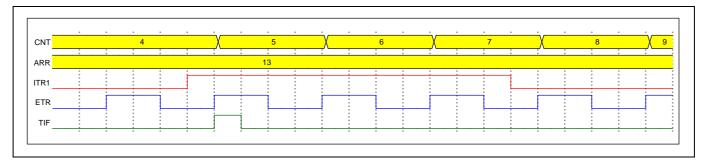

| Figure 10-34 Control time sequence in external clock mode 2 +slave mode (trigger mode) |     |

| Figure 10-35 Timer connectivity                                                        | 115 |

| Figure 10-36 Use master timer as slave timer prescaler                                 | 116 |

| Figure 10-37 Use master timer to enable slave timer                                    | 116 |

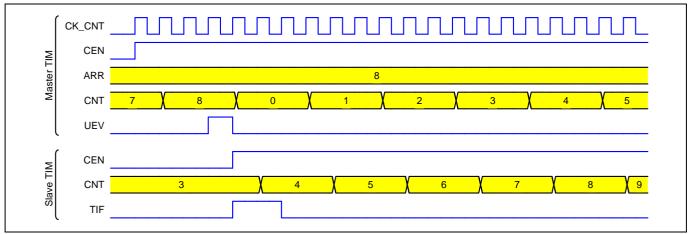

| Figure 10-38 Use master timer update event to start slave timer                        | 117 |

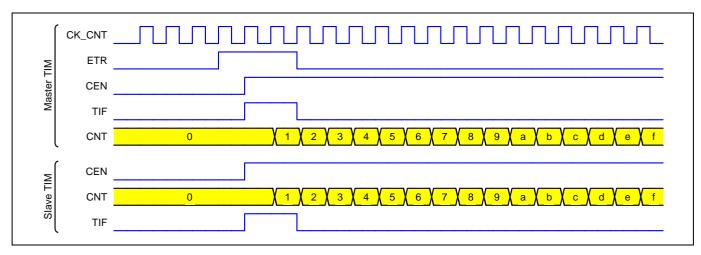

| Figure 10-39 master timer TI1 start master and slave timer in step                                       | 117        |

|----------------------------------------------------------------------------------------------------------|------------|

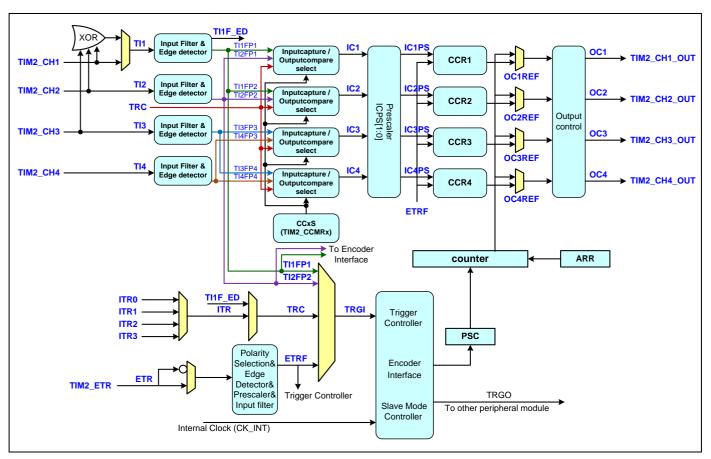

| Figure 11-1 TIMx block diagram                                                                           |            |

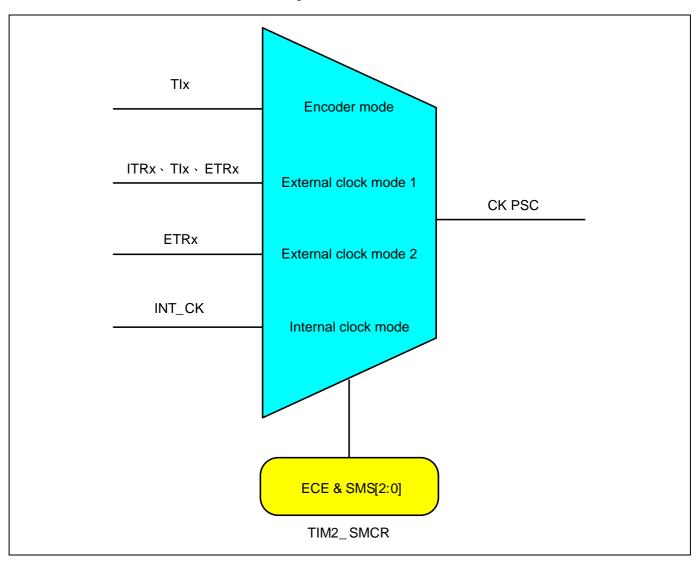

| Figure 11-2 Clock selection                                                                              | 139        |

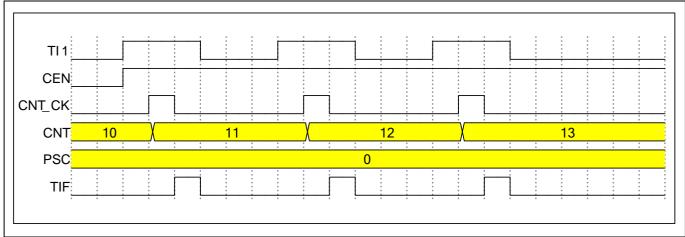

| Figure 11-3 Control circuit in external clock mode 1                                                     | 140        |

| Figure 11-4 Control circuit in external clock mode 2                                                     |            |

| Figure 11-5 Auto preload                                                                                 |            |

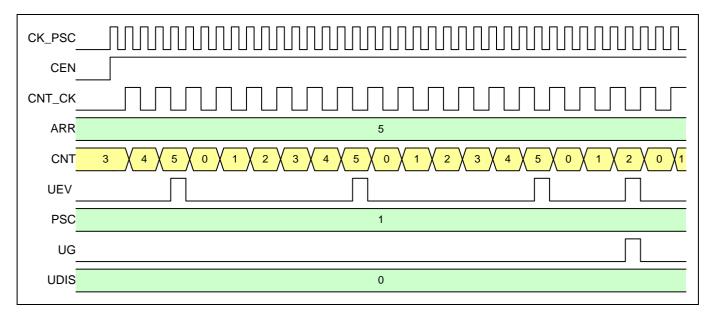

| Figure 11-6 Up counting mode (UDIS=0)                                                                    |            |

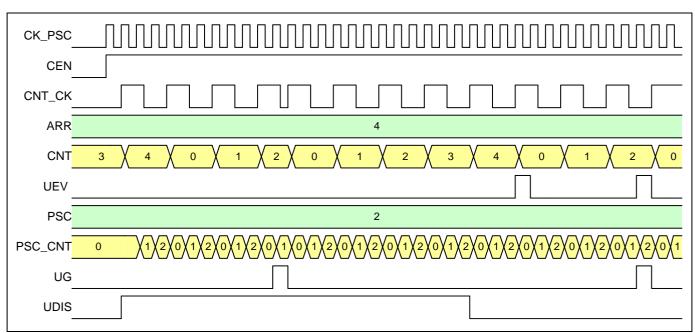

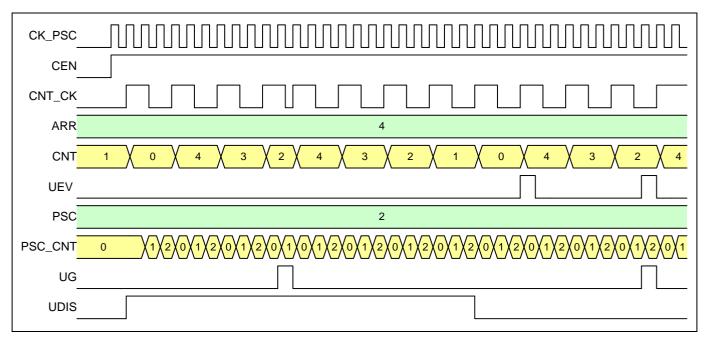

| Figure 11-7 Up counting mode (UDIS =1, disable update event)                                             | 142        |

| Figure 11-8 Down counting mode (UDIS=0)                                                                  | 142        |

| Figure 11-9 Down counting mode (UDIS=1 disables update event)                                            |            |

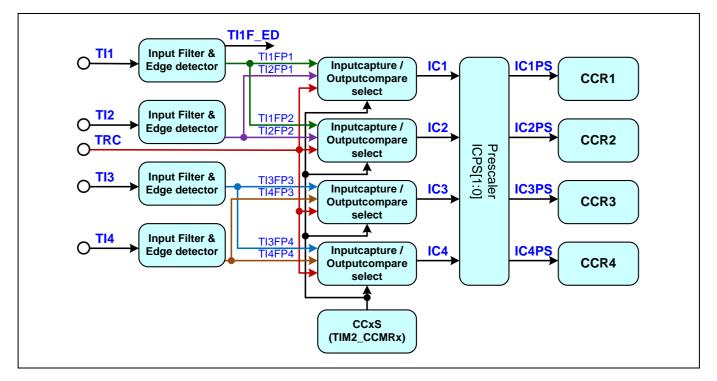

| Figure 11-10 Central count mode (UDIS=0)                                                                 |            |

| Figure 11-11 Central count mode (UDIS=1 disables update event)                                           |            |

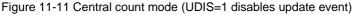

| Figure 11-12 TIMx input capture block diagram                                                            |            |

| Figure 11-13 PWM input mode sequence                                                                     |            |

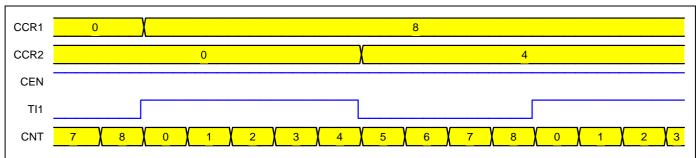

| Figure 11-14 Output compare block diagram                                                                |            |

| Figure 11-15 Output compare mode, OC1 signals toggle when match                                          |            |

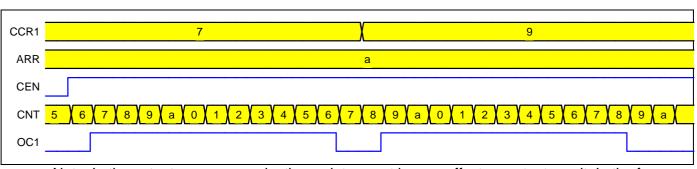

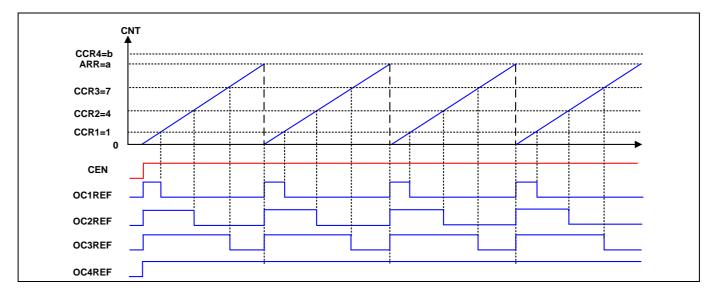

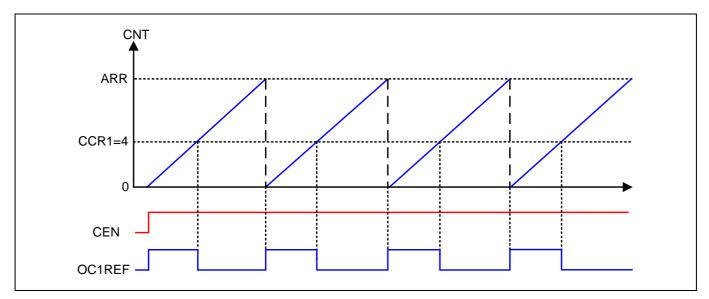

| Figure 11-16 Waveform in PWM mode 1 during edge alignment up count                                       |            |

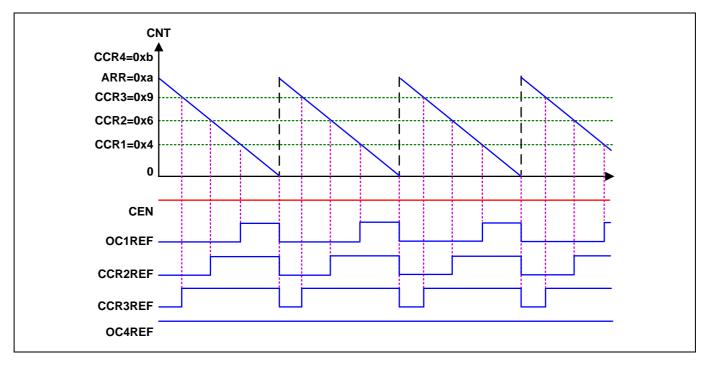

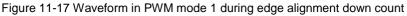

| Figure 11-17 Waveform in PWM mode 1 during edge alignment down count                                     |            |

| Figure 11-18 Waveform in central alignment PWM mode 1                                                    |            |

| Figure 11-19 example of CCx_SETTRGO output with edge aligned up counting mode                            |            |

| Figure 11-20 example of CCx_SETTRGO output with central alignment mode                                   |            |

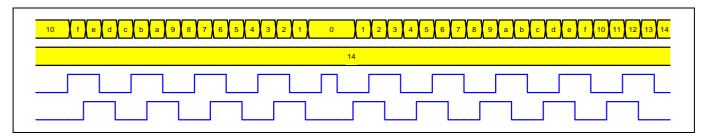

| Figure 11-21 The external event clear OCxREF                                                             |            |

| Figure 11-22 one-pulse mode                                                                              |            |

| Figure 11-23 Counter time sequence in the encoder code                                                   |            |

| Figure 11-24 IC1FP1 polarity inverted sequence of encoder interface mode                                 |            |

| Figure 11-25 Control time sequence of reset mode                                                         |            |

| Figure 11-26 Control time sequence of gate mode                                                          |            |

| Figure 11-27 Control time sequence of trigger mode                                                       |            |

| Figure 11-28 Control time sequence of external clock mode 2 +slave mode (trigger mode)                   |            |

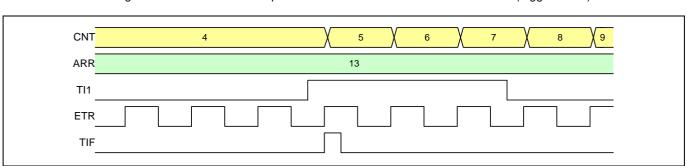

| Figure 11-29 (TI1 XOR input) input capture waveform                                                      |            |

| Figure 12-1 TIMx structure                                                                               |            |

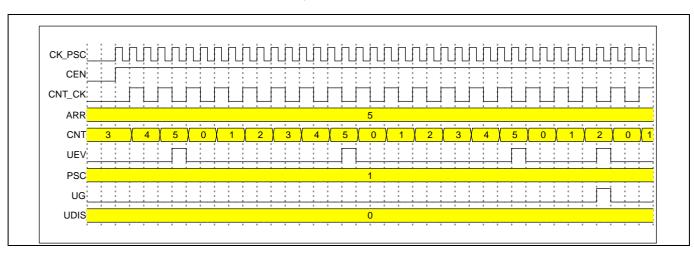

| Figure 12-2 Auto preload                                                                                 |            |

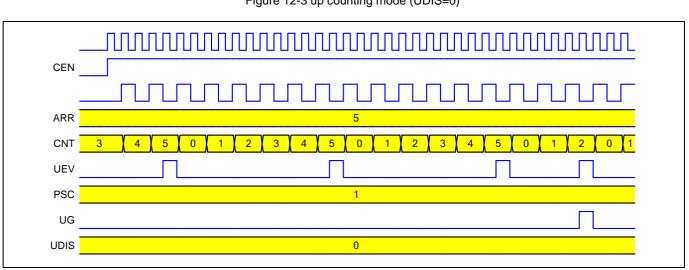

| Figure 12-3 up counting mode (UDIS=0)                                                                    |            |

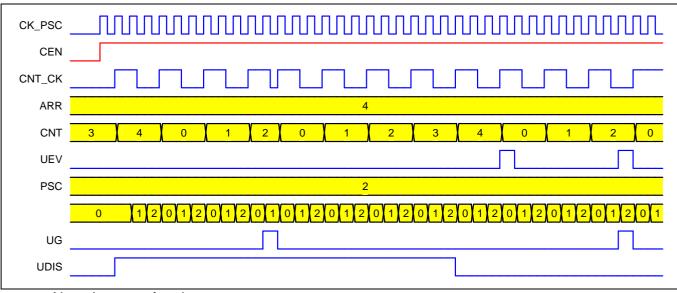

| Figure 12-4 up counting mode (UDIS =1, disable update event)                                             |            |

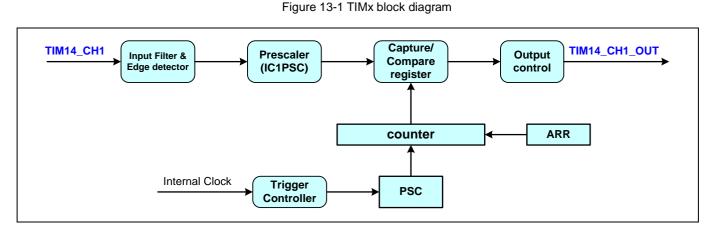

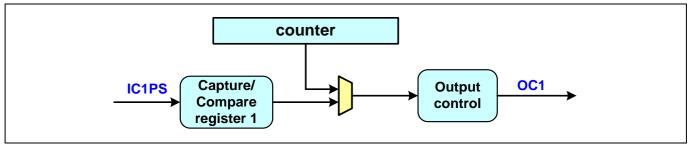

| Figure 13-1 TIMx block diagram                                                                           |            |

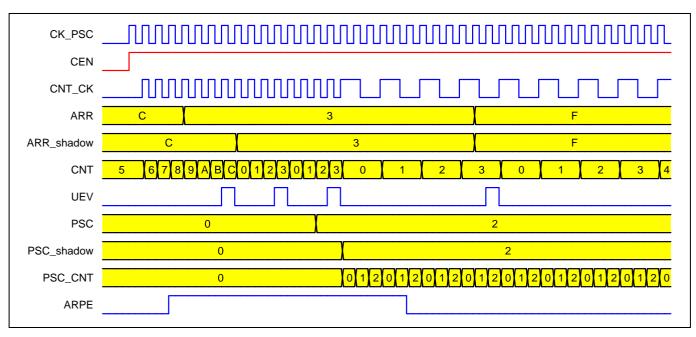

| Figure 13-2 Auto preload                                                                                 |            |

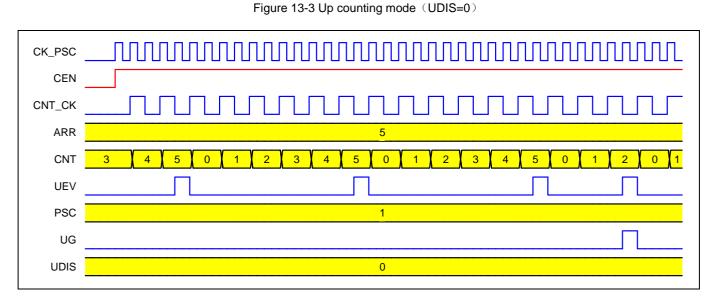

| Figure 13-3 Up counting mode (UDIS=0)                                                                    |            |

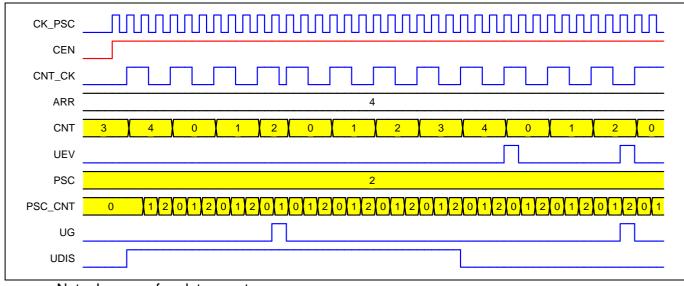

| Figure 13-4 Up counting mode (UDIS =1, disable update event)                                             |            |

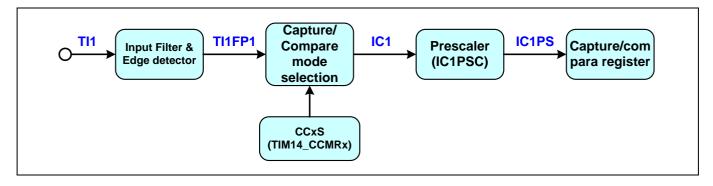

| Figure 13-5 TIMx input capture block diagram                                                             |            |

| Figure 13-6 Output compare block diagram                                                                 |            |

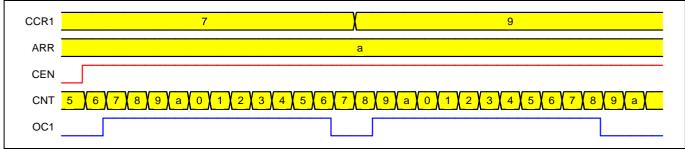

| Figure 13-7 Output compare mode, OC1 signals toggle when match                                           |            |

| Figure 13-8 Waveform in PWM mode 1 during edge alignment up count                                        |            |

| Figure 13-9 one-pulse mode                                                                               |            |

| Figure 14-1 Functional block diagram                                                                     |            |