### **BLDC ASIC Line**

# **MA853**

# One Hall for 3 phase brushless DC motor controller

**Data Sheet**

Version: 1.00

#### **Features**

MA853 is SIP chip, which has dual core (Arm® Cortex®-M0/ MCU and hardware motor controller/MCD) for 3 phase brushless DC motor controller with one hall sensor. Available in QFN32 (4x4x0.85mm) package.

#### MCU

- Cortex®-M0, frequency up to 48MHz.

- Memory (16KB embedded Flash storage and 2KB SRAM.)

- Built-in 48MHz HSI high-speed oscillator.

- Multiple low power modes include Sleep mode, Stop mode and Deep Stop mode.

- 5 timers:

- One 16-bit 4-channel advanced timer (TIM1), capable of generating four PWM outputs or three complementary PWM pairs, support center- or edge-aligned PWM mode, support hardware dead time insertion and fault brake, support PWM phase-shift output mode.

- One 16-bit 4-channel general purpose timer (TIM3), capable of generating four PWM outputs or capture four channel input signals, support decode of hall sensor and quadrature encoder, support infrared decode.

- One 16-bit basic timer (TIM14), capable of generating one PWM output or capture one channel input signal.

- One watchdog timer equipped with independent clock source (IWDG).

- One 24-bit Systick timer.

- Up to 10 fast I/O ports:

- All I/O ports can be mapped to 10 external interrupts.

- All I/O ports can accept input or generate output signal voltage level is not higher than VDD.

- One USART1.

- One 12-bit ADC (Analog-to-Digital converter) supports 1M SPS conversion rate, with 8 external inputs and 1 internal input that can sample on-chip voltage sensor.

- Embedded CRC engine

- Serial Wire Debug (SWD) for debug function.

- Operating temperature range includes -40°C ~ 105°C industrial tier.

#### MCD

- 1-Hall sine wave PWM drive

- Pre-driver for external N-ch MOSFET

- Closed loop speed control, configurable speed curve

- Adjustable driving current for the gate of external MOSFET

- Operating voltage range: 5 to 16 V

- Serial interface

- Standby mode

- Soft start

- Output RPM information

- Built-in protection features:

- Under Voltage Lock Out (UVLO), Under voltage protection for the charge pump,

- Over Voltage Protection (OVP), Lock detection, Thermal Shutdown (TSD),

Over Current limitation (OCL), Over current protection (ISD)

### **Contents**

| Fe     | ature | s                |                                                | 3  |

|--------|-------|------------------|------------------------------------------------|----|

| Сс     | ntent | s                |                                                | 5  |

| Та     | bles. |                  |                                                | 7  |

| Fic    | aures |                  |                                                | 9  |

| )<br>1 |       |                  | ction                                          |    |

| •      | 1.1   |                  | /iew                                           |    |

| 2      |       |                  | on Introduction                                |    |

| _      | 2.1   | Funct            | ion Block diagram                              | 11 |

|        | 2.2   |                  | Block diagram                                  |    |

|        | 2.3   |                  | Core introduction                              |    |

|        | 2.4   |                  |                                                |    |

|        | 2.5   |                  | Λ                                              |    |

|        | 2.6   |                  | ge regulator                                   |    |

|        | 2.7   |                  | r supply supervisors                           |    |

|        | 2.8   |                  | rs and watchdogs                               |    |

|        | 2.9   |                  | ·                                              |    |

|        | 2.10  | USAF             | RT                                             | 14 |

|        | 2.11  | ADC.             |                                                | 14 |

|        | 2.12  | CRC              |                                                | 14 |

|        | 2.13  | SWD              |                                                | 14 |

|        | 2.14  | MCD              | Block diagram                                  | 15 |

|        | 2.15  | MCD              | introduction                                   |    |

|        |       | 2.15.1           | MCD status                                     |    |

|        |       | 2.15.2           | 1-Hall commutation                             |    |

|        |       | 2.15.3           | PWM frequency                                  |    |

|        |       | 2.15.4           | Lead angle control                             |    |

|        |       | 2.15.5           | Soft Start                                     |    |

|        |       | 2.15.6           | Acceleration and deceleration control          |    |

|        |       | 2.15.7           | Output current for the gate of external MOSFET |    |

|        | 0.40  | 2.15.8           | Limitation of step of reducing rotation speed  |    |

|        | 2.16  |                  | Input / Output Signals                         |    |

|        |       | 2.10.1           |                                                |    |

|        |       | 2.16.2<br>2.16.3 | DIRALERT                                       |    |

|        |       | 2.16.3           | HP, HM                                         |    |

|        |       | 2.16.5           | FG                                             |    |

|        |       | 2.16.6           | BRAKE                                          |    |

|        | 2.17  |                  | Speed Control                                  |    |

|        | 2.17  | 2.17.1           | Closed loop                                    |    |

|        |       | 2.17.1           | Open loop                                      |    |

|        |       | 2.17.3           | Open/Close loop control with MCU               |    |

|        | 2.18  |                  | Serial I/F and NVM                             |    |

|        |       | 2.18.1           | Serial commands                                |    |

|        |       | 2.18.2           | Status register                                |    |

|        |       | 2.18.3           | Register map                                   |    |

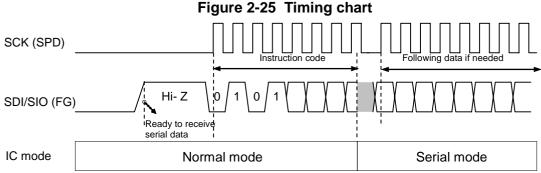

|        |       | 2.18.4           | Flowchart of writing Non-Volatile Memory (NVM) |    |

| 3      |       | Pinout           | and assignment                                 | 38 |

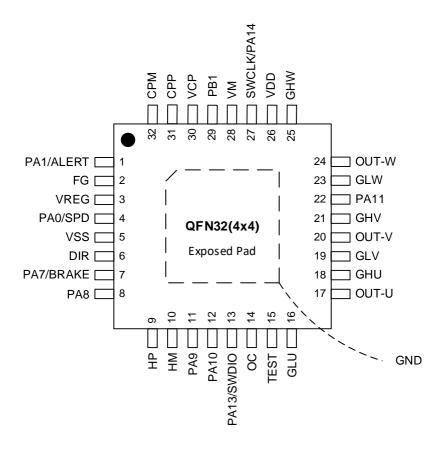

|        | 3.1   | QFN3             | 32 pinout                                      | 38 |

|        |       |                  |                                                |    |

#### **MA853**

|   | 3.2 | Pin as   | ssignment                                              | 39 |

|---|-----|----------|--------------------------------------------------------|----|

|   | 3.3 | Pin m    | nultiplexing                                           | 40 |

| 4 |     | Electric | cal Characteristics                                    | 41 |

|   | 4.1 |          | condition                                              |    |

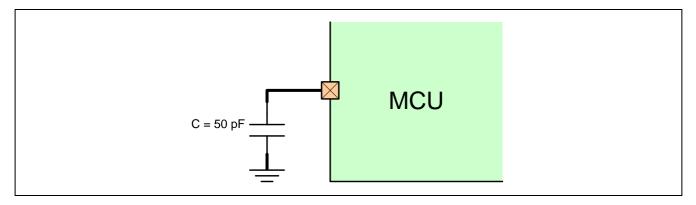

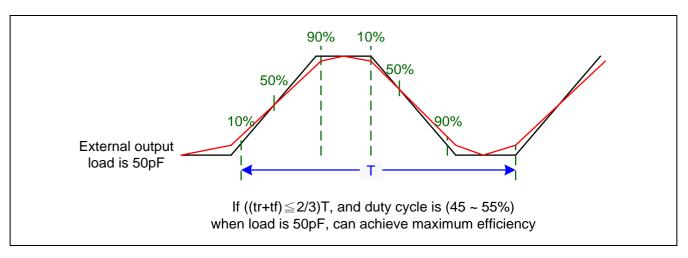

|   |     | 4.1.1    | Load capacitance                                       |    |

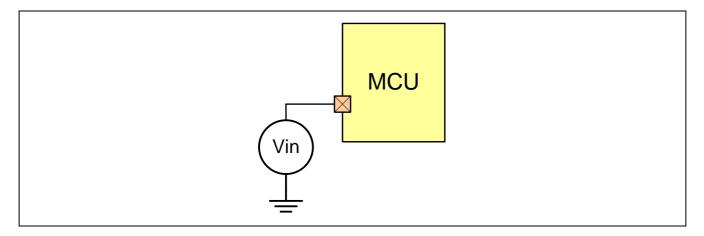

|   |     | 4.1.2    | I/O input voltage                                      |    |

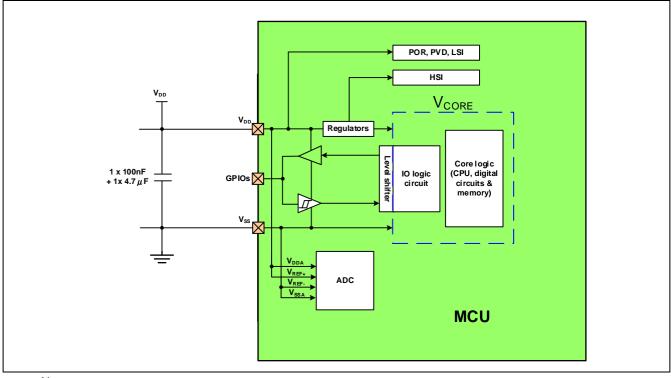

|   |     | 4.1.3    | Power scheme                                           |    |

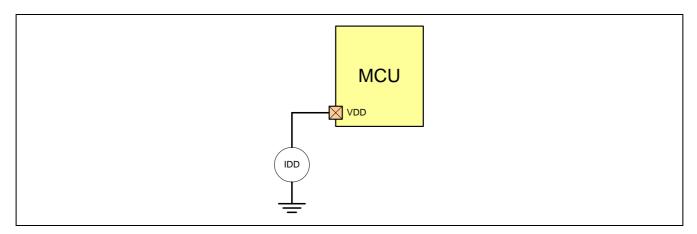

|   |     | 4.1.4    | Current consumption measurement                        |    |

|   | 4.2 | Absol    | lute maximum rating                                    | 43 |

|   | 4.3 | Opera    | ating conditions                                       | 44 |

|   |     | 4.3.1    | General operating conditions for MCU                   | 44 |

|   |     | 4.3.2    | Operating conditions at power-up/power-down for MCU    |    |

|   |     | 4.3.3    | Embedded reset and power control block characteristics |    |

|   |     | 4.3.4    | Built-in voltage reference                             |    |

|   |     | 4.3.5    | Supply current characteristics                         | 47 |

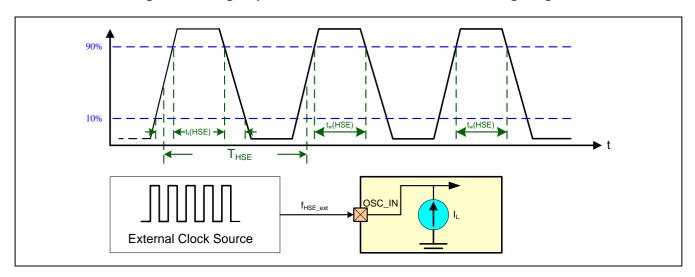

|   |     | 4.3.6    | External clock source characteristics                  | 50 |

|   |     | 4.3.7    | Internal clock source characteristics                  | 51 |

|   |     | 4.3.8    | Memory characteristics                                 | 51 |

|   |     | 4.3.9    | I/O port characteristics                               | 52 |

|   |     | 4.3.10   | Timer characteristics                                  | 53 |

|   |     | 4.3.11   | ADC characteristics                                    | 54 |

|   | 4.4 | Opera    | ation Range for MCD                                    | 57 |

|   |     | 4.4.1    | Electrical Characteristics for MCD                     | 57 |

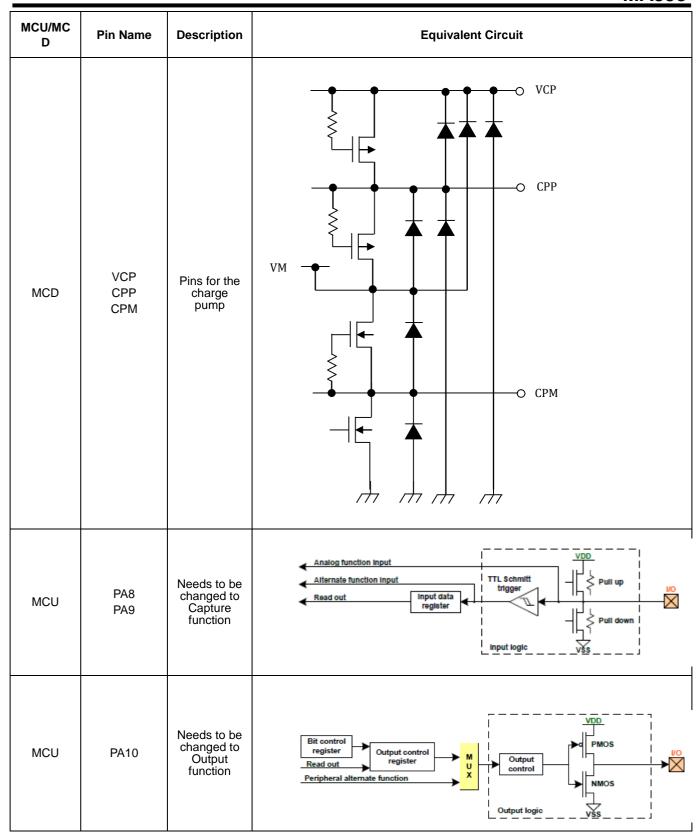

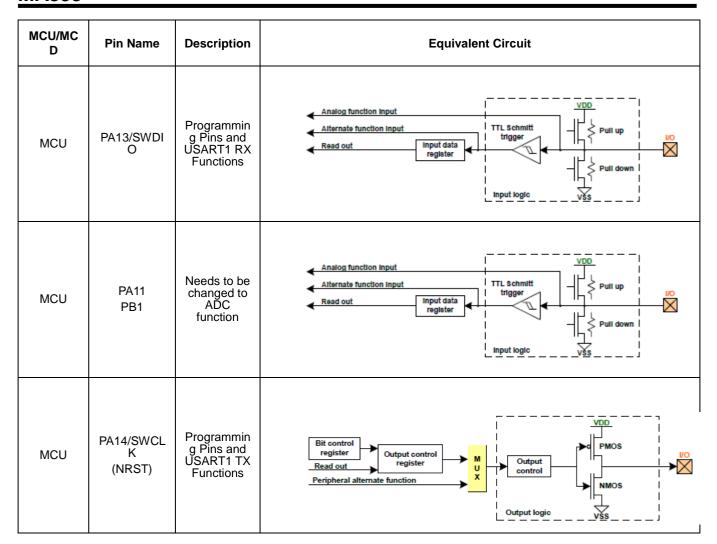

| 5 |     | I/O Equ  | iivalent Circuit                                       | 60 |

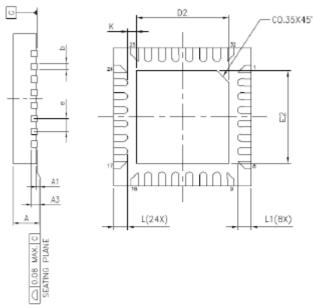

| 6 |     | Packag   | e dimensions                                           | 65 |

|   | 6.1 | _        | 32 (4x4x0.85mm)                                        |    |

| 7 |     | Revisio  | on history                                             | 66 |

| Ω |     | Disclair | mers                                                   | 67 |

### **Tables**

| Table 2-1 Feature summary of advanced, general purpose and basic timers                       | 12 |

|-----------------------------------------------------------------------------------------------|----|

| Table 2-2 MCD status in each mode                                                             | 16 |

| Table 2-3 Division ratio vs PWM frequency                                                     | 17 |

| Table 2-4 The setting of PWM frequency                                                        | 18 |

| Table 2-5 Table of LATABLE                                                                    | 18 |

| Table 2-6 The setting of controlling lead angle                                               | 19 |

| Table 2-7 The setting of the time for lock detecting in soft start                            | 20 |

| Table 2-8 Acceleration and deceleration rate                                                  |    |

| Table 2-9 Acceleration and deceleration control                                               |    |

| Table 2-10 Setting of source current for MOSFET                                               |    |

| Table 2-11 Setting of sink current for MOSFET                                                 |    |

| Table 2-12 The setting of step of speed                                                       |    |

| Table 2-13 Polarity of SPD                                                                    |    |

| Table 2-14 The relation of register and DIR                                                   |    |

| Table 2-15 The condition of low speed (Fault alarm) detection                                 |    |

| Table 2-16 Register setting vs FG and ALERT                                                   |    |

| Table 2-17 Relation of FG signal setting and the number of output pulses per one motor cycle  |    |

| Table 2-17 Relation of 1 9 signal setting and the number of output pulses per one motor cycle |    |

| Table 2-19 Lock detection setting during reverse brake                                        |    |

|                                                                                               |    |

| Table 2-20 Rotation Behavior (SPD signal value ≤ Startup point)                               |    |

| Table 2-21 Rotation Behavior (SPD signal value ≤ Startup point)                               |    |

| Table 2-22 Serial commands (Instruction Code)                                                 |    |

| Table 2-23 Status Register (SR)                                                               |    |

| Table 2-24 Register map                                                                       |    |

| Table 3-1 Pin assignment table                                                                |    |

| Table 3-2 PA port multiplexing AF0-AF4                                                        |    |

| Table 4-1 Voltage characteristics for MCU                                                     |    |

| Table 4-2 Current characteristics for MCU                                                     |    |

| Table 4-3 Absolute Maximum Ratings for MCD                                                    |    |

| Table 4-4 General operating conditions                                                        |    |

| Table 4-5 Operating conditions at power-up/power-down                                         |    |

| Table 4-6 Embedded reset and power control block characteristics                              | 45 |

| Table 4-7 Build-in voltage reference                                                          |    |

| Table 4-8 Typical current consumption in Run mode                                             | 47 |

| Table 4-9 Typical current consumption in Sleep mode                                           |    |

| Table 4-10 Typical current consumption in stop mode (1)                                       |    |

| Table 4-11 On-chip peripheral current consumption (1)                                         | 49 |

| Table 4-12 Wake up time from low power mode                                                   | 50 |

| Table 4-13 High-speed external user clock characteristics                                     | 50 |

| Table 4-14 HSI oscillator characteristics (1)                                                 | 51 |

| Table 4-15 LSI oscillator characteristics (1)                                                 | 51 |

| Table 4-16 Flash memory characteristics                                                       | 51 |

| Table 4-17 Flash memory endurance and data retention (1)(2)                                   | 52 |

| Table 4-18 I/O static characteristics                                                         |    |

| Table 4-19 Output voltage static characteristics                                              | 52 |

| Table 4-20 I/O AC characteristics (1)(2)                                                      |    |

| Table 4-21 TIMx <sup>(1)</sup> characteristics                                                |    |

| Table 4-22 ADC characteristics                                                                |    |

| Table 4-23 Maximum RAIN at fADC = 15MHz <sup>(1)</sup>                                        |    |

| Table 4-24 ADC static parameters (1)(2)                                                       |    |

| Table 4-25 Operating Ranges for MCD                                                           |    |

| Table 4 20 Operating Italigue for info                                                        |    |

### **MA853**

| Table 4-26 | NVM Characteristics for MCD        | 57 |

|------------|------------------------------------|----|

|            | Electrical Characteristics for MCD |    |

| Table 4-28 | Serial I/F for MCD                 | 59 |

|            | evision history                    |    |

### **Figures**

| Figure 2-1 Function Block Diagram                                                                  | 11  |

|----------------------------------------------------------------------------------------------------|-----|

| Figure 2-2 MCU Block Diagram                                                                       | 11  |

| Figure 2-3 MCD Block Diagram                                                                       | 15  |

| Figure 2-4 Basic operation flow chart                                                              | 16  |

| Figure 2-5 Timing chart of Hall input signal and sine-wave commutation signal                      | 17  |

| Figure 2-6 Timing chart of Hall input and 150° commutation signal                                  | 17  |

| Figure 2-7 Example of the setting of lead angle LATABLE = 14 (1b01110)                             | 18  |

| Figure 2-8 Example of the setting of lead angle LATABLE = 4 (1b00100)                              | 19  |

| Figure 2-9 Timing chart of soft start                                                              | 19  |

| Figure 2-10 Example of DUTYCHGLIMIT = 2                                                            | 20  |

| Figure 2-11 Diagram of reaching a target speed                                                     | 21  |

| Figure 2-12 Hall signal waveform                                                                   | 24  |

| Figure 2-13 Hall and FG signal waveform                                                            | 24  |

| Figure 2-14 Waveform of Hall signal and induced voltage in CW                                      | 24  |

| Figure 2-15 The waveform of Hall signal and induced voltage in CCW                                 | 24  |

| Figure 2-16 Example of the default position of Hall element                                        | 24  |

| Figure 2-17 Speed slope example in closed loop control                                             | 27  |

| Figure 2-18 Speed Slope Example in Closed loop speed control (in case of adding speed change point | .28 |

| Figure 2-19 Speed Slope Example in Closed loop speed control (in case of DIR50=1)                  | 29  |

| Figure 2-20 Speed slope example in Open loop speed control                                         | 30  |

| Figure 2-21 Speed Slope Example in Open loop speed control (in case of adding speed change point)  | 31  |

| Figure 2-22 Speed Slope Example in Open loop speed control (in case of DIR50=1)                    | 32  |

| Figure 2-23 Open loop speed control with multi speed changing points by MCU                        | 33  |

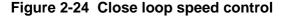

| Figure 2-24 Close loop speed control                                                               | 33  |

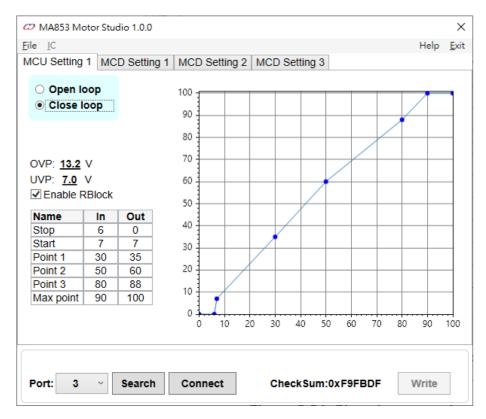

| Figure 2-25 Timing chart                                                                           | 34  |

| Figure 2-26 NVM writing flowchart                                                                  | 37  |

| Figure 3-1 QFN32 pinout diagram                                                                    | 38  |

| Figure 4-1 Load condition of the pin                                                               |     |

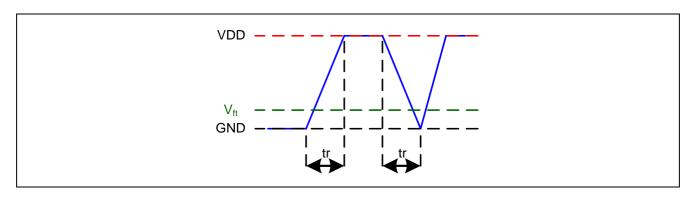

| Figure 4-2 Pin input voltage                                                                       | 41  |

| Figure 4-3 Power scheme (1)                                                                        | 42  |

| Figure 4-4 Current consumption measurement scheme                                                  | 42  |

| Figure 4-5 Power-on and power-down waveforms                                                       | 45  |

| Figure 4-6 High-speed external clock source AC timing diagram                                      | 50  |

| Figure 4-7 I/O AC characteristics                                                                  | 53  |

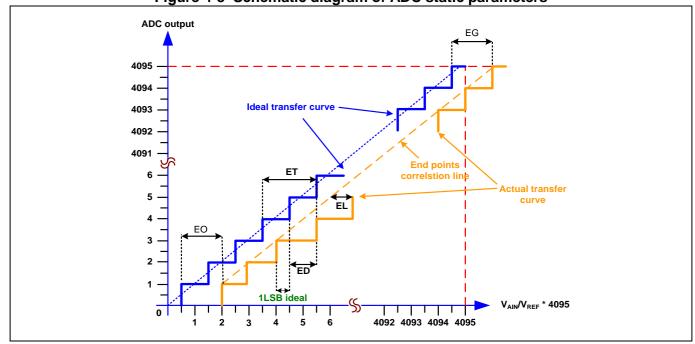

| Figure 4-8 Schematic diagram of ADC static parameters                                              | 56  |

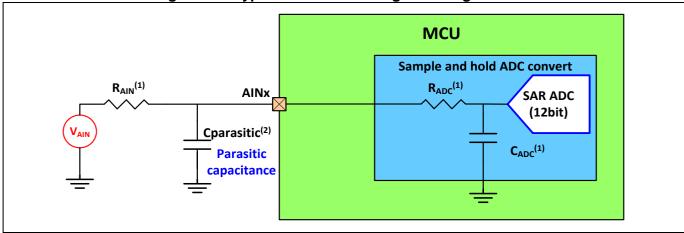

| Figure 4-9 Typical connection diagram using the ADC                                                |     |

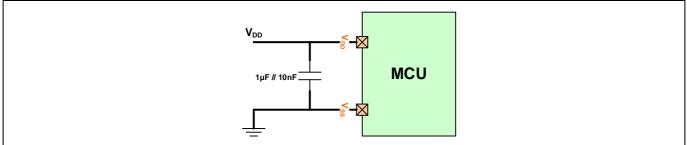

| Figure 4-10 Power supply and reference power supply decoupling circuit                             |     |

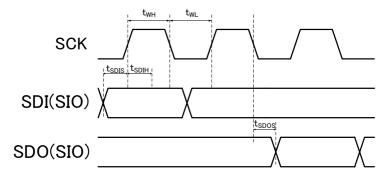

| Figure 4-11 Serial I/F timing chart                                                                |     |

| Figure 6-1 OFN32 package dimension                                                                 | 65  |

### 1 Introduction

#### 1.1 Overview

The MA853 has dual core (Arm® Cortex®-M0/MCU and hardware motor controller/MCD) for 3 phase brushless DC motor controller. The MCD can be operated by 1-Hall sine-wave commutation and 1-Hall 150° commutation. Also, a closed loop speed control function is implemented without using an external microcontroller. Motor rotation speed can be controlled by inputting PWM signal or applying analog voltage to the SPD pin. The operation moves to the standby mode when a zero cross of the Hall signal is not detected for a lock detection period after the voltage of VSTBY(L) or less is applied to the SPD pin. In the standby mode, the IC power consumption is reduced by powering off its internal 5-V regulator. In case that the Hall element is power supplied by the IC's 5-V regulator, the power consumption of the whole motor system can be reduced. In case that motor is configured as not stop when the voltage of SPD pin is VSTBY(L) or less, standby mode is disabled.

The MCU has a maximum clocked frequency of 48MHz, built-in 16KB Flash storage, and contains an extensive range of peripherals and I/O ports. It contains one 12-bit ADC, one 16-bit advanced timer, one 16-bit general purpose timer and one 16-bit basic timer, as well as communication interface including one USART. The operating voltage of MCU is 2.0V to 5.5V, and the operating temperature range (ambient temperature) is -40°C to 105°C extended industrial tier.

MA853 has dual cores, MCD and MCU. The MCD core can run motor control well. And the MCU has more I/O for the flex control behaviors and can assist MCD in more themes. This device is available in QFN32 (4x4x0.85 mm).

## **2** Function Introduction

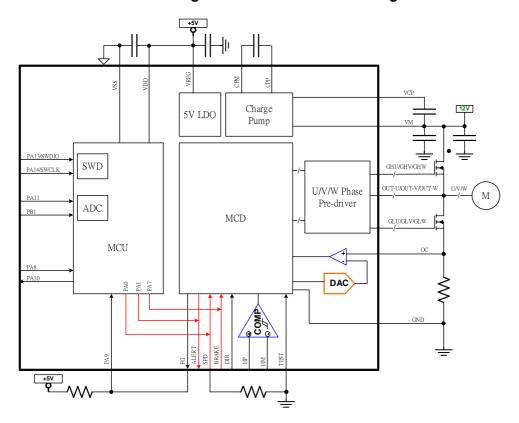

#### 2.1 Function Block diagram

Figure 2-1 Function Block Diagram

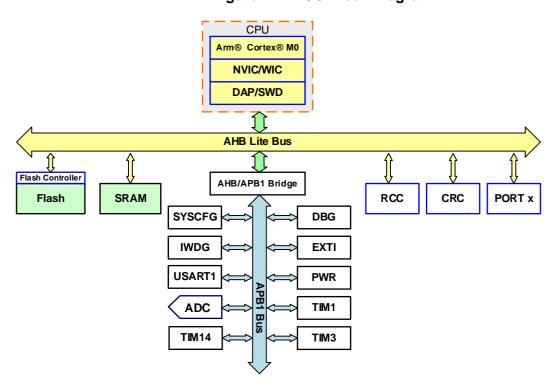

#### 2.2 MCU Block diagram

Figure 2-2 MCU Block Diagram

#### 2.3 MCU Core introduction

The Arm® Cortex®-M0 processor provides real-time processing and advanced interrupt handling system, which is perfect for cost-effective and low-pin-count microcontrollers targeting real-time control and low power applications.

The Arm® Cortex®-M0 is a 32-bit RISC processor, provides state-of-the-art code efficiency, which is extremely suitable for small memory size microcontrollers and small code size applications.

#### 2.4 Flash

This product provides up to 16KB embedded Flash memory available for storing code and data.

#### 2.5 SRAM

This product provides up to 2KB embedded SRAM.

#### 2.6 Voltage regulator

The on-chip voltage regulator can regulate the external supply voltage to a lower and stable supply voltage that used by the internal circuits. The voltage regulator is workable after the chip power-on reset (POR).

#### 2.7 Power supply supervisors

This product integrates the power-on reset (POR) and power-down reset (PDR) circuit. This circuit is workable in all power modes, to make sure the chip can work above the lowest power supply voltage. When the  $V_{DD}$  is lower than the preset threshold ( $V_{POR}/V_{PDR}$ ), this circuit will put system to reset status.

This product also integrates a programmable voltage monitor (PVD), it can monitor the  $V_{DD}$  and  $V_{DDA}$  voltage, and compare it with the preset threshold  $V_{PVD}$ . When  $V_{DD}$  is lower or higher than  $V_{PVD}$ , an interrupt request can be generated, then the interrupt handler can send out warning information or put the chip into safe mode. The PVD function can be configured to be enabled.

#### 2.8 Timers and watchdogs

This product has one advanced timer, one general purpose timer, one basic timer, one watchdog timer and one Systick timer. The table below compares the features of advanced, general purpose and basic timers.

Table 2-1 Feature summary of advanced, general purpose and basic timers

| Туре            | Instance | Resolution | Counter direction    | pre-divider | DMA request | Capture/compare channels | Complementary output |

|-----------------|----------|------------|----------------------|-------------|-------------|--------------------------|----------------------|

| Advanced        | TIM1     | 16-bit     | up, down,<br>up/down | 1 to 65536  | No          | 4 (no capture)           | 3                    |

| General purpose | TIM3     | 16-bit     | up, down,<br>up/down | 1 to 65536  | No          | 4                        | No                   |

| Basic           | TIM14    | 16-bit     | up                   | 1 to 65536  | No          | 1                        | No                   |

#### Advanced timer (TIM1)

The advanced timer includes a 16-bit counter, four capture/compare channels and three phases complementary PWM generator. This timer supports hardware dead-time insertion when using as complementary PWM generator. This timer can also be used as a full-function general purpose timer. This timer has four independent channels, each channel can be used for:

- Output compare

- PWM generator (center- or edge-aligned)

#### Single pulse output

When this timer is used as a general-purpose timer, it has the same function as the TIM2. When this timer is used as a 16-bit PWM generator, it can be configured to a broad duty cycle range from 0% to 100%.

In debug mode, the counter can be frozen.

The advanced timer has lots of identical features and internal structures as the general-purpose timer, in this way the advanced timer can work together with the general-purpose timer through the link function, to provide synchronization and event trigger function.

#### **General-purpose timer (TIM3)**

This product has one general-purpose timer (TIM3). The timer has a 16-bit counter, support both up and down counting, with automatically reload. The timer also has a 16-bit frequency pre-divider and four independent channels. Each channel can be used as input capture, output compare, PWM or single pulse output. These general-purpose timers can also work together through the timer link function, to provide synchronization between timers and event trigger function.

These timers can also be used to decode incremental encoder signals and can also be used to decode one to four Hall sensors' digital output. Any general-purpose timer can be used to generate PWM output or work as basic timer.

In debug mode, the counter can be frozen.

#### **Basic timer (TIM14)**

This product has one 16-bit basic timer (TIM14). Each timer has one 16-bit counter, supporting only up counting, with automatically reload. The timer also has one 16-bit frequency pre-divider and one independent channel. Each channel can be used as input capture, output compare, PWM or one pulse mode output.

#### Independent watchdog (IWDG)

The independent watchdog is based on a 12-bit down counter and an 8-bit prescaler. It is clocked by an internal independent 40KHz oscillator. As it is independent of the main clock, it can run in shutdown and standby modes. It can be used to reset the entire system when a system error occurs or as a free timer to provide timeout management for applications. It can be configured to start the watchdog by software or hardware through the option byte. In debug mode, the counter can be frozen.

#### System tick timer (Systick)

This timer is dedicated to the real-time operating system and can also be used as a general down counter. It has the following features:

- 24-bit down counter

- Auto-reload capability

- A makeable interrupt can be generated when counter value is 0

- Programmable clock source

#### 2.9 **GPIO**

Each GPIO pin can be configured by software as output (push-pull or open-drain), input (with or without pull-up or pull-down) or multiplexed peripherals function port. Most GPIO pins are shared with digital or analog functions.

If necessary, the peripheral functions of the I/O pins can be locked by specific operation to avoid accidental writing to the I/O register.

#### **2.10 USART**

This product has one Universal Synchronous/Asynchronous Receiver/Transmitter (USART) interfaces. The USART provides flexibility for full-duplex data exchange with peripherals using the industry standard NRZ asynchronous serial data format. This module can support a wide range of baud rates through the integrated baud rate generator (including integer and fraction settings). Support LSB or MSB receive/transmit mode. Support 8- or 9-bit programmable data length. Support 0.5-/1-/1.5-/2-bit stop bit configuration. The USART can support synchronous or asynchronous one-way communication and half-duplex single-wire communication. Support maximum 6Mbps baud rate.

#### 2.11 ADC

This product has one 12-bit analog/digital converter (ADC), support up to 1Msps conversion rate, with up to two external channels and one internal channel available. Support single-shot single-cycle and continuous scan conversion. Support any sequence sampling mode, the sampling channels can be sequenced in any order. One internal channel is used to sample the built-in voltage reference, and in application the voltage level of the chip power supply can be derived from the sampled conversion value.

The analog watchdog function allows the application to monitor one or all selected channels. When the monitored signal exceeds a preset threshold, an interrupt will be generated.

The triggers generated by the general-purpose timers and the advanced timers can be selected to trigger the ADC sampling, in this way the ADC sampling can be synchronized with the timer.

#### 2.12 CRC

The cyclic redundancy check (CRC) module uses a fixed polynomial generator to generate a CRC code from a 32-bit data word. Among many applications, CRC is used to verify the consistency of data transmission or storage. Within the scope of the EN/IEC60335-1 standard, it provides a method to detect flash memory errors. The CRC module can be used to calculate the signature of the software package in real time and compare it with the signature generated when the software is linked and generated.

#### 2.13 SWD

This product equips ARM standard Serial Wire Debug (SWD).

#### 2.14 MCD Block diagram

VМ VCP **UVLO ISD** 5V VREG Charge CPP Pump OCP TSD CPM ALERT Control Logic Gate Driver SPD Nonvolatile Memory (NVM) **ADC** SDO Serial SDI SCK I/F GND DIR HP Position Detect НМ

Figure 2-3 MCD Block Diagram

#### 2.15 MCD introduction

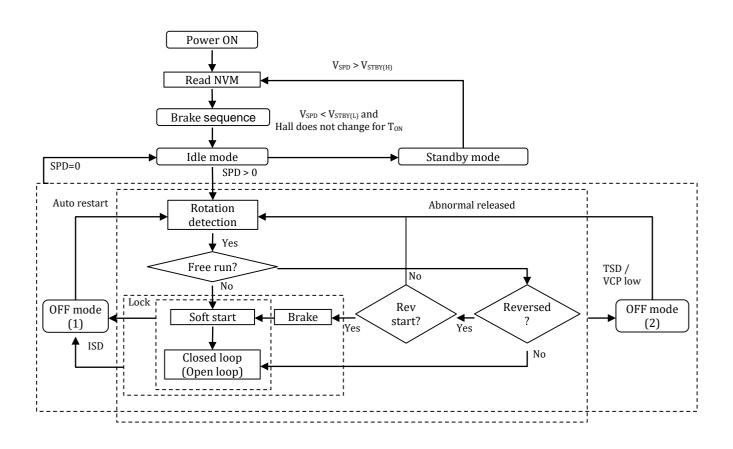

MCD can be operated by 1-Hall sine-wave commutation and 1-Hall 150° commutation. Also, a closed loop speed control function is implemented without using an external microcontroller. Motor rotation speed can be controlled by inputting PWM signal or applying analog voltage to the SPD pin.

The operation moves to the standby mode when a zero cross of the Hall signal is not detected for a lock detection period after the voltage of  $V_{STBY(L)}$  or less is applied to the SPD pin. In the standby mode, the IC power consumption is reduced by powering off its internal 5 V regulator. In case that the Hall element is power supplied by the IC's 5 V regulator, the power consumption of the whole motor system can be reduced. In case that motor is configured as not stop when the voltage of SPD pin is  $V_{STBY(L)}$  or less, standby mode is disabled.

Figure 2-4 Basic operation flow chart

2.15.1 MCD status

Table 2-2 MCD status in each mode

|                                      |     | Read<br>NVM        | Stop<br>mode                    | OFF mode<br>(1)  | OFF mode<br>(2)                 | Standby<br>mode | Normal<br>mode                                                       |  |

|--------------------------------------|-----|--------------------|---------------------------------|------------------|---------------------------------|-----------------|----------------------------------------------------------------------|--|

| VREG                                 |     | 5V                 | 5V                              | 5V               | 5V                              | OFF             | 5V                                                                   |  |

| Charge pu                            | mp  | Active             | Active                          | Active           | Active                          | Inactive        | Active                                                               |  |

| FG                                   | FG  | During reading: L  | Hall output<br>(Hi-Z under 1Hz) | Hi-Z             | Hall output<br>(Hi-Z under 1Hz) | Hi-Z            | Hall output<br>(Hi-Z under 1Hz)                                      |  |

| function                             | RDO | After reading:Hi-Z | State sustaining                | State sustaining | State sustaining                | Hi-Z            | Lock is detected:L<br>Lock is released:Hi-Z                          |  |

| ALERT                                |     | Hi-Z               | State sustaining<br>(Note 1)    | L (Note 3)       | L (Note 3)                      | Hi-Z            | Fault (Note 2) is<br>detected: L (Note 3)<br>Fault is released: Hi-Z |  |

| GLx (x: U, V, W)<br>GHx (x: U, V, W) |     | L                  | L                               | L                | L                               | Hi-Z            | Active                                                               |  |

Note 1: ALERT = L when TSD / VCP is dropped. ALERT is released when the cause of fault is released.

Note 2: Fault means ISD / TSD / VCP dropping and lock.

Note 3: When ALERTINV = 0. ALERT outputs H level when ALERTINV = 1.

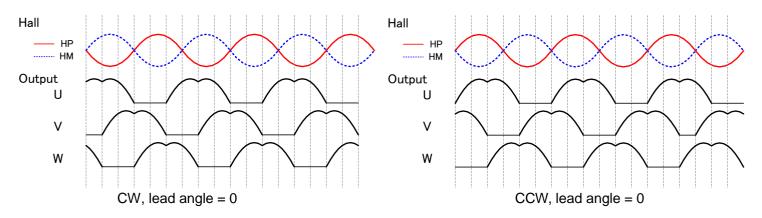

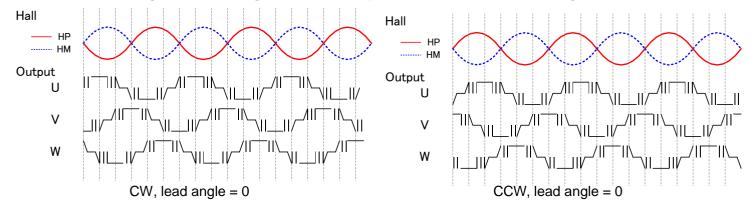

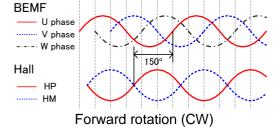

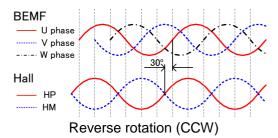

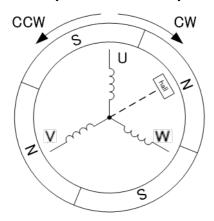

#### 2.15.2 1-Hall commutation

MCD can be operated by 1-Hall sine-wave commutation and 1-Hall 150° commutation.

The type of commutation can be switched by register.

Rotation direction is defined by DIR and register setting.

Figure 2-5 Timing chart of Hall input signal and sine-wave commutation signal

Figure 2-6 Timing chart of Hall input and 150° commutation signal

#### 2.15.3 PWM frequency

PWM is generated from internal oscillator.

Table 2-3 Division ratio vs PWM frequency

| Division ratio | PWM frequency |

|----------------|---------------|

| 512            | 23.4kHz       |

| 256            | 46.9kHz       |

| 128            | 93.7kHz       |

| 64             | 187.5kHz      |

Table 2-4 The setting of PWM frequency

|              |   |          |            |             |              | f <sub>hall</sub> |              |            |  |  |

|--------------|---|----------|------------|-------------|--------------|-------------------|--------------|------------|--|--|

| PWMSEL [2:0] |   | 0 to 250 | 250 to 500 | 500 to 1000 | 1000 to 1500 | 1500 to 2000      | Over 2000    |            |  |  |

|              |   |          | 150 to 0   | 400 to 150  | 900 to 400   | 1400 to 900       | 1900 to 1400 | Under 1900 |  |  |

| 0            | 0 | 0        |            | 23.4kHz     |              |                   |              |            |  |  |

| 0            | 0 | 1        |            | 46.9kHz     |              |                   |              |            |  |  |

| 0            | 1 | 0        |            | 93.7kHz     |              |                   |              |            |  |  |

| 0            | 1 | 1        |            |             | 1            | 87.5kHz           |              |            |  |  |

| 1            | 0 | 0        | 23.4kHz    | 23.4kHz     | 46.9kHz      | 46.9kHz           | 93.7kHz      | 93.7kHz    |  |  |

| 1            | 0 | 1        | 23.4kHz    | 46.9kHz     | 46.9kHz      | 93.7kHz           | 93.7kHz      | 187.5kHz   |  |  |

| 1            | 1 | 0        | 23.4kHz    | 46.9kHz     | 93.7kHz      | 93.7kHz           | 187.5kHz     | 187.5kHz   |  |  |

| 1            | 1 | 1        | 46.9kHz    | 93.7kHz     | 93.7kHz      | 187.5kHz          | 187.5kHz     | 187.5kHz   |  |  |

Note: There is a 100Hz hysteresis when the motor decreases its speed.

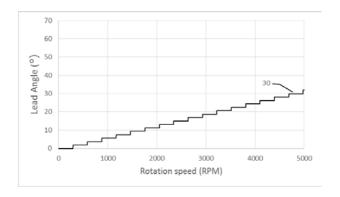

#### 2.15.4 Lead angle control

MCD contains the function of lead angle control.

This function requires a Hall signal to compensate the lead angle with the setting of LATABLE.

Table 2-5 Table of LATABLE

| LATABLE [4:0] |   |   |   |   | The value of lead angle                                                                     |  |

|---------------|---|---|---|---|---------------------------------------------------------------------------------------------|--|

| 0             | 0 | 0 | 0 | 0 | LATABLE = 0 to 27                                                                           |  |

|               |   |   |   |   | Lead angle (deg) = 1.875 (deg) x Speed (RPM) / 4096 x LATABLE Maximum lead angle is 58.125° |  |

| 1             | 1 | 0 | 1 | 1 |                                                                                             |  |

| 1             | 1 | 1 | 0 | 0 | 7.5° fixed                                                                                  |  |

| 1             | 1 | 1 | 0 | 1 | 15° fixed                                                                                   |  |

| 1             | 1 | 1 | 1 | 0 | 22.5° fixed                                                                                 |  |

| 1             | 1 | 1 | 1 | 1 | 30° fixed                                                                                   |  |

Figure 2-7 Example of the setting of lead angle LATABLE = 14 (1b01110)

70 60 50 9 40 40 40 8 30 9 20 10 0 5000 1000 15000 20000 Rotation speed (RPM)

Figure 2-8 Example of the setting of lead angle LATABLE = 4 (1b00100)

This IC features Intelligent Phase control (InPAC), which can automatically optimize lead angle by comparing the zero-cross timing of the hall signal with the zero-cross timing of the motor current.

Table 2-6 The setting of controlling lead angle

| LASEL | Auto          |

|-------|---------------|

| 0     | InPAC enable  |

| 1     | InPAC disable |

InPAC is enabled when LASEL=0.

Lead angle=Optimized lead angle by InPAC + lead angle set in LATABLE

Since a low motor current in low speed makes a difficulty of detecting zero cross, InPAC regards an optimized lead angle is zero when the motor speed becomes under startup frequency.

When LASEL=1, InPAC is disabled, and an optimized lead angle is zero.

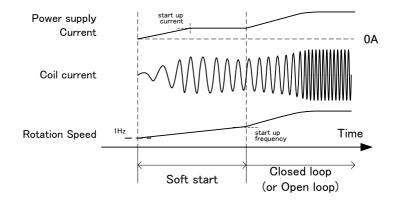

#### 2.15.5 Soft Start

Soft start operates when the motor starts from the stop state to prevent rush current.

Figure 2-9 Timing chart of soft start

Soft start increases the output duty gradually from 0 % until the output current reaches the startup current. The rotation frequency increases from 1 Hz.

Soft start is finished and switches to the closed loop speed control or the open loop speed control when the rotation frequency reaches the switching frequency (startup frequency).

The way of commutation is defined by register setting.

The time for lock detecting in soft start can be selected by register setting so that slow start motor can be used.

Table 2-7 The setting of the time for lock detecting in soft start

| SS_LOCK | The time for lock detecting (s) |

|---------|---------------------------------|

| 0       | TON x 1                         |

| 1       | TON x 5                         |

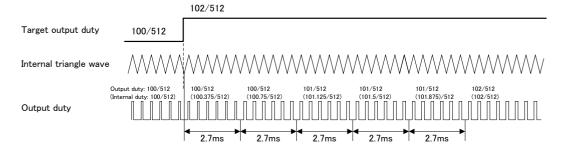

#### 2.15.6 Acceleration and deceleration control

Acceleration and deceleration rate of motor can be controlled by limiting of PWM duty.

Table 2-8 Acceleration and deceleration rate

| Duty change limit<br>( DUTYCHGLIMIT ) | Variation amount of duty<br>every 2.7ms (Δ/512) | Time (sec)<br>from 0% to 100% |

|---------------------------------------|-------------------------------------------------|-------------------------------|

| 0                                     | N/A (64/8)                                      | 0.17                          |

| 1                                     | 2/8                                             | 5.53                          |

| 2                                     | 3/8                                             | 3.69                          |

| 3                                     | 4/8                                             | 2.76                          |

| 4                                     | 6/8                                             | 1.84                          |

| 5                                     | 10/8                                            | 1.11                          |

| 6                                     | 20/8                                            | 0.55                          |

| 7                                     | 56/8                                            | 0.20                          |

Figure 2-10 Example of DUTYCHGLIMIT = 2

Table 2-9 Acceleration and deceleration control

| Item Soft start          |                               | Closed loop    |                                                                     |  | Onen leen      | Mild brake     | Reverse brake  |

|--------------------------|-------------------------------|----------------|---------------------------------------------------------------------|--|----------------|----------------|----------------|

| Item                     | Soit Start                    | Acceleration   | Steady Deceleration                                                 |  | Open loop      | Willa brake    | Reverse brake  |

| Period of changing duty  | 2.7 ms                        | 10.8 or 2.7 ms | 2.7 ms                                                              |  | 10.8 or 2.7 ms | 10.8 or 2.7 ms | 10.8 or 2.7 ms |

| Variation amount of duty | Duty chg limit for soft start | Duty chg limit | Determined by PI<br>(Maximum variation<br>amount is Duty chg limit) |  | Duty chg limit | Duty chg limit | Duty chg limit |

#### 2.15.7 Output current for the gate of external MOSFET

MCD drives external MOSFETs. This IC contains six half bridge pre-drivers and drives high-side and low-side Nch-MOSFETs. The voltage for high-side gate of MOSFET is  $V_M + 8V(typ.)$ . The voltage for low-side gate of MOSFET is 8 V(typ.). The register, ISOURCE\_SEL, ISINK\_SEL set a driving current to the gate.

Table 2-10 Setting of source current for MOSFET Table 2-11 Setting of sink current for MOSFET

| ISOURCE_SEL [2:0] | Source current (mA) |

|-------------------|---------------------|

| 000               | 10.0                |

| 001               | 13.9                |

| 010               | 19.3                |

| 011               | 26.8                |

| 100               | 37.3                |

| 101               | 51.8                |

| 110               | 72.0                |

| 111               | 100.0               |

| ISINK_SEL [2:0] | Sink current (mA) |

|-----------------|-------------------|

| 000             | 20.0              |

| 001             | 27.8              |

| 010             | 38.6              |

| 011             | 53.7              |

| 100             | 74.6              |

| 101             | 103.6             |

| 110             | 143.9             |

| 111             | 200.0             |

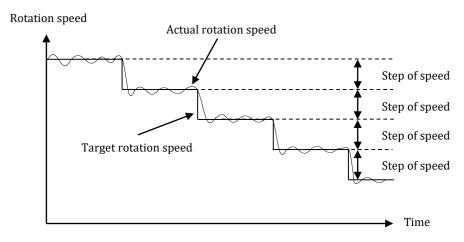

#### 2.15.8 Limitation of step of reducing rotation speed

Limiting the step of reducing rotation speed, motor locking can be avoided.

Table 2-12 The setting of step of speed

| RPMLIMIT[2:0] | Step of speed(rpm) |

|---------------|--------------------|

| 000           | No limit           |

| 001           | 512                |

| 010           | 2200               |

| 011           | 3800               |

| 100           | 5400               |

| 101           | 7000               |

| 110           | 8600               |

| 111           | 10240              |

Figure 2-11 Diagram of reaching a target speed

#### 2.16 MCD Input / Output Signals

#### 2.16.1 SPD

SPD pin controls the motor start, the motor stop, and the rotation speed.

PWM duty signal input or analog voltage signal input can be configured by the register. Also, the polarity of the signal can be configured by the register.

Table 2-13 Polarity of SPD

|                      | Positive logic (Default)                                                      | Negative logic                                                                               |

|----------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Analog voltage input | $V_{VSP(L)}$ : SPD command = 0 (0%)<br>$V_{VSP(H)}$ : SPD command = 512(100%) | V <sub>VSP(L)</sub> : SPD command = 512 (100%)<br>V <sub>VSP(H)</sub> : SPD command = 0 (0%) |

| PWM duty input       | H active                                                                      | L active (Note 1)                                                                            |

Note 1: The polarity of the input signal is inverted inside the IC, and the inverted signal is used as the positive logic SPD.

In case of analog voltage input, the resolution is 9-bit in the voltage range of  $V_{VSP(L)}$  to  $V_{VSP(H)}$ . In case of PWM duty input, its frequency range is from 1 kHz to 100 kHz. When the frequency range is from 1 kHz to 20 kHz, the resolution is 9-bit. And when it is 20 kHz or more, the resolution decreases. For example, in case of 40 kHz, the resolution is 8-bit, and in case of 100 kHz, it becomes 7-bit. In addition, the SPD pin can be also used as the clock input pin for the serial interface (for SCK signal).

#### 2.16.2 DIR

DIR pin controls the motor rotation direction; forward rotation (CW) and reverse rotation (CCW). Relation of DIR pin polarity and the rotation direction is configured by the register.

Table 2-14 The relation of register and DIR

| Register (DIR) | DIR pin | Rotation direction |

|----------------|---------|--------------------|

| 0              | L       | CW                 |

|                | Н       | CCW                |

| 1              | L       | CCW                |

|                | Н       | CW                 |

#### 2.16.3 ALERT

ALERT pin is an open drain type output pin. When an abnormal state (over current, over temperature, motor lock, or under voltage for charge pump) is detected, this pin outputs low signal. In addition, this pin can be also used as the data output pin for serial interface (for SDO signal) when the serial interface is 3 lines type. If a serial interface has 2 lines, ALERT pin outs only ALERT signal. The fault alarm which means low speed activates when the starting rotation speed which is set by STARTRPM is the number which is described in table below over ten seconds. Fault alarm is released when the rotation speed reaches over 70% of the STARTRPM.

Table 2-15 The condition of low speed (Fault alarm) detection

| Starting rotation speed setting | Threshold of detection |

|---------------------------------|------------------------|

| STARTRPM ≥ 1000rpm              | STARTRPM x 50%         |

| 700rpm ≥ STARTRPM > 1000rpm     | STARTRPM – 500rpm      |

| 288rpm ≥ STARTRPM > 700rpm      | 200rpm                 |

| STARTRPM < 288 rpm              | Do not detect          |

ALERT pin signal is defined as table below.

Table 2-16 Register setting vs FG and ALERT

|       | Register F |          | FG output signal (Note1)   |          | ALERT output signal (Note 2)                                                  |          |

|-------|------------|----------|----------------------------|----------|-------------------------------------------------------------------------------|----------|

| RDSEL | ALRMSEL    | ALERTINV | Signal                     | Polarity | Signal                                                                        | Polarity |

| 0     | 0          | 0        | FG                         | _        | Lock / Low voltage of charge<br>pump / ISD / TSD                              | L        |

| 0     | 0          | 1        | FG                         | _        | Lock / Low voltage of charge pump / ISD / TSD                                 | Н        |

| 0     | 1          | 0        | FG                         | _        | Low speed (Fault alarm) / Low<br>voltage of charge pump / ISD /<br>TSD(Note3) | L        |

| 0     | 1          | 1        | FG                         | _        | Low speed (Fault alarm) / Low<br>voltage of charge pump / ISD /<br>TSD(Note3) | Н        |

| 1     | 0          | 0        | Lock                       | L        | Lock / Low voltage of charge pump / ISD / TSD                                 | L        |

| 1     | 0          | 1        | Lock                       | L        | Lock / Low voltage of charge pump / ISD / TSD                                 | Н        |

| 1     | 1          | 0        | Low speed<br>(Fault alarm) | L        | Low speed (Fault alarm) / Low<br>voltage of charge pump / ISD /<br>TSD(Note3) | L        |

| 1     | 1          | 1        | Low speed<br>(Fault alarm) | L        | Low speed (Fault alarm) / Low<br>voltage of charge pump / ISD /<br>TSD(Note3) | Н        |

Note 1: When FG pin signal is lock or Low speed (Fault alarm), its polarity is always "L", and the level of signal is "L". FG pin outs "L" in 3ms when the power on or reboot from STBY mode.

Note 2: When REVALERT is set to "1", ALERT signal is out in the reverse rotation detection.

Note 3: Low speed (Fault alarm) / Low voltage of charge pump / ISD / TSD(Note3) appear immediately after failure occurring.

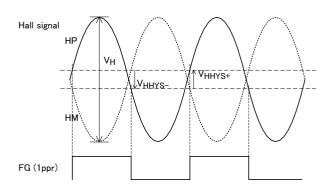

#### 2.16.4 HP, HM

Pins of HP and HM are input pins for Hall signals.

In case of using Hall element, please input signals whose characteristics are shown below.

Figure 2-12 Hall signal waveform

HP Common phase input voltage range

HP HM GND

Figure 2-13 Hall and FG signal waveform

In case of using Hall IC, the Hall signal must be input to HP pin. Voltage of HM pin should be fixed.

As default, please align the Hall sensor so that the relationship between Hall signals and induced voltage is as charts below.

Figure 2-14 Waveform of Hall signal and induced voltage in CW

Figure 2-15 The waveform of Hall signal and induced voltage in CCW

Figure below is the example of the default Hall position.

Figure 2-16 Example of the default position of Hall element

#### 2.16.5 FG

FG pin is an open drain type output pin. It outputs the rotation speed signal that is obtained from the Hall signal. According to the register setting, FG pin can also output RDO signal when motor lock is detected. RDO signal is low level in motor lock detection.

In addition, FG pin can be also used as the data input or input/output pin for serial interface (for SDI or SIO signal).

1 ppr (pulse per revolution), 3ppr, 2.4ppr, 0.5ppr can be selected as FG signal. Below table show the number of FG pulse per 1 rotation of motor.

Table 2-17 Relation of FG signal setting and the number of output pulses per one motor cycle

| F00F1 [2:01 | FG signal setting | Number of motor poles |         |         |         |          |

|-------------|-------------------|-----------------------|---------|---------|---------|----------|

| FGSEL [2:0] |                   | 2 poles               | 4 poles | 6 poles | 8 poles | 10 poles |

| 000         | 1 ppr             | 1                     | 2       | 3       | 4       | 5        |

| 001         | 2/3 ppr           | 2/3                   | 4/3     | 2       | 8/3     | 10/3     |

| 010         | 1/2 ppr           | 0.5                   | 1       | 1.5     | 2       | 2.5      |

| 011         | 2 ppr             | 2                     | 4       | 6       | 8       | 10       |

| 100         | 3 ppr             | 3                     | 6       | 9       | 12      | 15       |

| 101         | 2.4 ppr           | 2.4                   | 4.8     | 7.2     | 9.6     | 12       |

| 110         | 1/3 ppr           | 1/3                   | 2/3     | 1       | 4/3     | 5/3      |

| 111         | Don't use         |                       |         |         |         |          |

Note: FG pin outputs the signal when the frequency of the Hall signal is 1Hz or more.

When the frequency of the Hall signal is less than 1Hz, FG signal is fixed to Hi-Z.

Note: When FG signal is set to 1 ppr, a signal synchronized with the Hall signal is output.

When FG signal is set to the others, internal processed result is output.

FG pin can be also used as the data input pin for serial interface (for SDI signal) when the serial interface is 3 lines type. If a serial interface has 2 lines, FG pin can be also used as the data input/output pin for serial interface (for SIO).

#### 2.16.6 BRAKE

BRAKE pin is for controlling the motor braking function. MCD has several braking functions, motor off, short brake, reverse brake, mild brake.

Table 2-18 Brake function setting

| BRAKE pin | Regis                | Motor status           |               |

|-----------|----------------------|------------------------|---------------|

|           | BRK_INV              | BRK_INV BRK_MODE [1:0] |               |

| L         | 0: Positive polarity | Don't care             | No brake      |

| L         | 1: Negative polarity | 00                     | No brake      |

| L         | 1: Negative polarity | 01                     | Short brake   |

| L         | 1: Negative polarity | 10                     | Reverse brake |

| L         | 1: Negative polarity | 11                     | Mild brake    |

| Н         | 0: Positive polarity | 00                     | No brake      |

| Н         | 0: Positive polarity | 01                     | Short brake   |

| Н         | 0: Positive polarity | 10                     | Reverse brake |

| Н         | 0: Positive polarity | 11                     | Mild brake    |

| Н         | 1: Negative polarity | Don't care             | No brake      |

Table 2-19 Lock detection setting during reverse brake

| Driving status right after power on | BRAKEALT   | ALRMSEL    | Flag output on ALERT pin                      |

|-------------------------------------|------------|------------|-----------------------------------------------|

| Short brake                         | Don't care | Don't care | Low voltage of charge pump / ISD / TSD        |

| Reverse brake                       | 0          | 0          | Low voltage of charge pump / ISD / TSD        |

| Reverse brake                       | 1          | 0          | Lock / Low voltage of charge pump / ISD / TSD |

| Reverse brake                       | Don't care | 1          | Low voltage of charge pump / ISD / TSD        |

| Mild brake                          | Don't care | Don't care | Low voltage of charge pump / ISD / TSD        |

#### 2.17 MCD Speed Control

#### 2.17.1 Closed loop

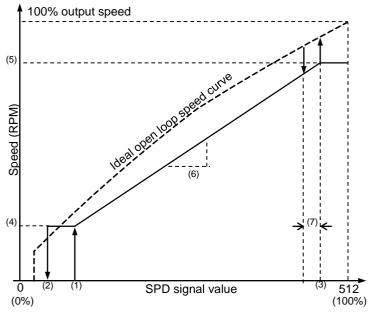

The basic speed curve (relation between SPD signal value and rotation speed) of closed loop speed control is as follows.

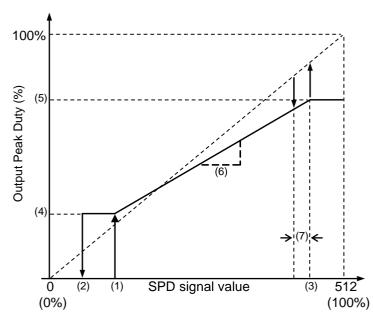

Figure 2-17 Speed slope example in closed loop control

- (1) Startup point

- (2) Stop point

- (3) Output clamping point

- (4) Startup speed

- (5) Maximum speed (depending on speed slope)

- (6) Speed slope

- (7) MAXOPEN hysteresis

Please set as follows.

$(3) > (1) \ge (2)$

(1) Startup point:

Output is enabled when SPD signal value exceeds the startup threshold. The threshold range is from 0 (0 %) to 255 (49.8 %) with a 0.2 % resolution. It is set by the 8-bit register STARTDUTY. SPD duty to enable output (%) =  $100 \times STARTDUTY / 512$

#### (2) Stop point:

Output is disabled when SPD signal value decreases to the stop threshold. The threshold range is from 0 (0 %) to 254 (49.6 %) with a 0.4 % resolution. It is set by the 7-bit register STOPDUTY.  $SPD\ duty\ to\ disable\ output\ (\%) = 200\ x\ STOPDUTY/512$

#### (3) Output clamping point and (7) MAXOPEN hysteresis:

In case MAXDUTY = 0: When SPD signal value exceeds the output clamping threshold, the rotation speed is fixed. The threshold range is from 257 (50.2 %) to 512 (100 %) with a 0.2 % resolution. It is set by the 8-bit register MAXDUTY.

SPD duty to clamp output (%) =  $100 \times (257 + MAXDUTY) / 512$

In case MAXOPEN = 1: When SPD signal value exceeds the output clamping threshold, the control switches to open loop speed control. The output duty during open loop speed control corresponds to SPD signal value. The hysteresis of SPD signal value to let the control switch back to closed loop speed control range is from 2 (0.4 %) to 32 (6.25 %) with a 0.4 % resolution. It is set by the 4-bit register MAXDUTYHYS.

SPD duty hys (%) =  $200 \times (MAXDUTYHYS + 1) / 512$

#### (4) Startup speed:

The minimum rotation speed in startup is set by the 12-bit register STARTRPM. Setting range is from 0 to 4095 RPM with 1 RPM resolution.

Startup speed (RPM) = STARTRPM

#### (5) Maximum speed and (6) Speed slope:

Maximum speed depends on the speed slope, which is set by the register SPEEDSLOP. It is a 14-bit register.

SPEEDSLOP = 64 x (Maximum speed - Startup speed) / (MAXDUTY + 257 - STARTDUTY)

Configurations of MAXOPEN, NOSTOP, and MAXOFF registers determine the behavior when SPD signal value is equivalent to the startup (output enabling) point or less.

Table 2-20 Rotation Behavior (SPD signal value ≤ Startup point)

| MAYODEN | NOSTOP | MAXOFF | Target speed  |                              |                                        |  |

|---------|--------|--------|---------------|------------------------------|----------------------------------------|--|

| MAXOPEN |        |        | SPD =0 %      | 0 % < SPD<br>≤ Startup point | Stop point < SPD<br>≤ Startup point    |  |

|         | 0      | 0      | 0             | 0                            | Duty up: 0<br>Duty down: Startup speed |  |

| 0       | 0      | 1      | Maximum Speed | 0                            | Duty up: 0<br>Duty down: Startup speed |  |

|         | 1      | 0      | Startup speed | Startup speed                | Startup speed                          |  |

|         | 1      | 1      | Maximum Speed | Maximum Speed                | Startup speed                          |  |

| 1       | 0      | 0      | 0             | 0                            | Duty up: 0<br>Duty down: Startup speed |  |

|         | 0      | 1      | 100 % Output  | 0                            | Duty up: 0<br>Duty down: Startup speed |  |

|         | 1      | 0      | Startup speed | Startup speed                | Startup speed                          |  |

|         | 1      | 1      | 100 % Output  | 100 % Output                 | Startup speed                          |  |

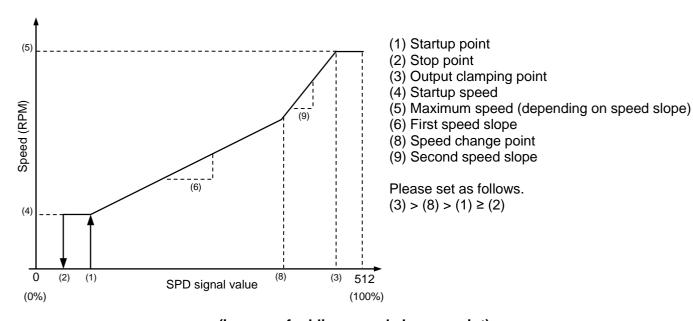

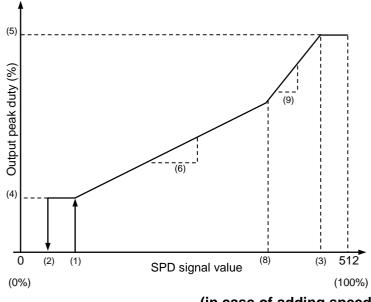

Adding a speed change point to the speed curve is possible.

Figure 2-18 Speed Slope Example in Closed loop speed control

#### (in case of adding speed change point)

#### (8) Speed change point:

The SPD signal value range of the speed change point is from 0 (0.4 %) to 510 (99.6 %) with a 0.4 % resolution. It is set by the 8-bit register CHANGEDUTY. SPD duty of change point (%) =  $200 \times CHANGEDUTY / 512$

In case of not using the speed change point, set CHANGEDUTY to 0.

#### (9) Second speed slope:

After passing the speed change point, the register SPEEDSLOP2 sets the speed slope.

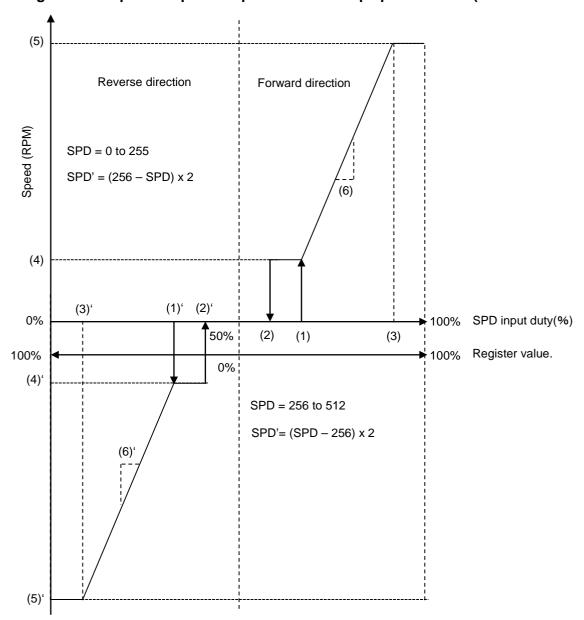

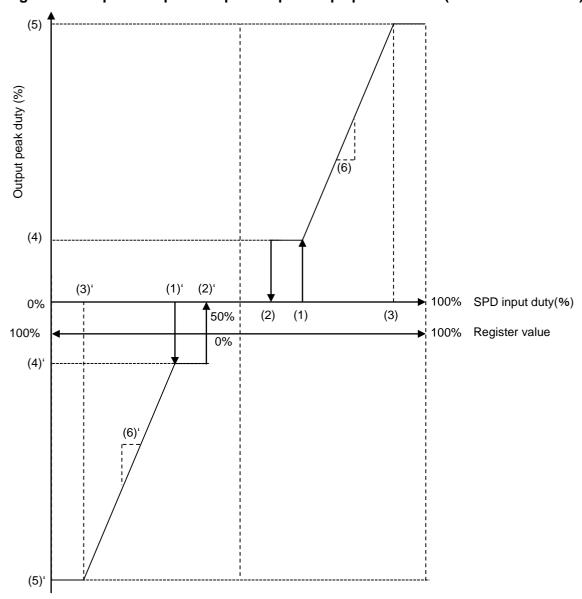

In case of DIR50=1, rotation direction of motor is controlled by the duty of SPD signal. Motor rotates forward direction when SPD duty is 50% or more. Motor rotates reverse direction when SPD duty is under 50%.

Figure 2-19 Speed Slope Example in Closed loop speed control (in case of DIR50=1)

#### 2.17.2 Open loop

The basic speed curve (relation between SPD signal value and output duty) of open loop speed control is as follows.

Figure 2-20 Speed slope example in Open loop speed control

- (1) Startup point

- (2) Stop point

- (3) Output clamping point

- (4) Startup output duty

- (5) Maximum output duty (depending on speed slope)

- (6) Speed slope

- (7) MAXOPEN hysteresis

Please set as follows.

$(3) > (1) \ge (2)$

#### (1) Startup point:

Output is enabled when SPD signal value exceeds the startup threshold. The threshold range is from 0 (0 %) to 255 (49.8 %) with a 0.2 % resolution. It is set by the 8-bit register STARTDUTY. SPD duty to enable output (%) = 100 x STARTDUTY/512

#### (2) Stop point:

Output is disabled when SPD signal value decreases to the stop threshold. The threshold range is from 0 (0 %) to 254 (49.6 %) with a 0.4 % resolution. It is set by the 7-bit register STOPDUTY. SPD duty to disable output (%) =  $200 \times STOPDUTY / 512$

#### (3) Output clamping point and (7) MAXOPEN hysteresis:

In case MAXDUTY = 0: When SPD signal value exceeds the output clamping threshold, the output duty is fixed. The threshold range is from 257 (50.2 %) to 512 (100 %) with a 0.2 % resolution. It is set by the 8-bit register MAXDUTY.

SPD duty clamp output (%) =  $100 \times (257 + MAXDUTY) / 512$

In case MAXOPEN = 1: When SPD signal value exceeds the output clamping threshold, the output duty becomes corresponding to SPD signal value. The hysteresis range of SPD signal value to let the output return to original speed curve is from 2 (0.4 %) to 32 (6.25 %) with a 0.4 % resolution. It is set by the 4-bit register MAXDUTYHYS.

SPD duty hys (%) =  $200 \times (MAXDUTYHYS + 1) / 512$

#### (4) Startup output duty:

The minimum output duty in startup is set by an upper 8-bit of the 12-bit register STARTRPM. Setting range is from 0 (0 %) to 255 (49.8 %) with a 0.2 % resolution.

Startup output duty (%) =  $100 \times STARTRPM [11:4] / 512$

#### (5) Maximum output duty and (6) Speed slope:

Maximum output duty depends on the speed slope, which is set by the register SPEEDSLOP. It is a 14-bit register.

$SPEEDSLOP = 2^{19} \times (Maximum \ output \ duty \ (\%) - Startup \ output \ duty \ (\%)) / (MAXDUTY + 257 - STARTDUTY) / 100.$

Configurations of MAXOPEN, NOSTOP, and MAXOFF registers determine the behavior when SPD signal value is equivalent to the startup (output enabling) point or less.

Table 2-21 Rotation Behavior (SPD signal value ≤ Startup point)

| MAXOPEN | NOSTOP | MAXOFF | Output Duty    |                              |                                         |  |

|---------|--------|--------|----------------|------------------------------|-----------------------------------------|--|

|         |        |        | SPD =0 %       | 0 % < SPD<br>≤ Startup point | Stop point < SPD<br>≤ Startup point     |  |

|         | 0      | 0      | 0              | 0                            | Duty up: 0<br>Duty down: Startup Output |  |

| 0       | 0      | 1      | Maximum Output | 0                            | Duty up: 0<br>Duty down: Startup Output |  |

|         | 1      | 0      | Startup Output | Startup Output               | Startup Output                          |  |

|         | 1      | 1      | Maximum Output | Maximum Output               | Startup Output                          |  |

| 1       | 0      | 0      | 0              | 0                            | Duty up: 0<br>Duty down: Startup Output |  |

|         | 0      | 1      | 100 % Output   | 0                            | Duty up: 0<br>Duty down: Startup Output |  |

|         | 1      | 0      | Startup Output | Startup Output               | Startup Output                          |  |

|         | 1      | 1      | 100 % Output   | 100 % Output                 | Startup Output                          |  |

Adding a speed change point to the speed curve is possible.

Figure 2-21 Speed Slope Example in Open loop speed control

- (1) Startup point

- (2) Stop point

- (3) Output clamping point

- (4) Startup output duty

- (5) Maximum output duty (depending on speed slope)

- (6) First speed slope

- (8) Speed change point

- (9) Second speed slope

Please set as follows.

$(3) > (8) > (1) \ge (2)$

(in case of adding speed change point)

#### (8) Speed change point:

The SPD signal value range of the speed change point is from 0 (0.4 %) to 510 (99.6 %) with a 0.4 % resolution. It is set by the 8-bit register CHANGEDUTY.

SPD duty of change point (%) = 200 x CHANGEDUTY / 512

In case of not using the speed change point, set CHANGEDUTY to 0.

#### (9) Second speed slope:

After passing the speed change point, the register SPEEDSLOP2 sets the speed slope.

megawin Version: 1.00 31

In case of DIR50=1, rotation direction of motor is controlled by the duty of SPD signal. Motor rotates forward direction when SPD duty is 50% or more. Motor rotates reverse direction when SPD duty is under 50%,

Figure 2-22 Speed Slope Example in Open loop speed control (in case of DIR50=1)

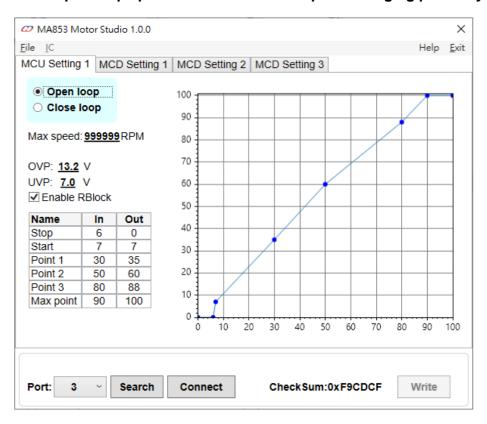

#### 2.17.3 Open/Close loop control with MCU

Based on MCD open loop control, MCU can support more speed changing points by MA853 motor Studio as shown as **Figure 2-23**.

MCU detects SPD signal and converts the input duty to output duty by curve table. The curve table can set to MCU by MA853 Motor Studio. And MCU has ADC to measure supply voltage for OVP(Over-voltage protect) and UVP(Under-voltage protect).

Based on MCD close loop control, MCU only set OVP/UVP and RBlock function as shown as **Figure 2-24**.

Figure 2-23 Open loop speed control with multi speed changing points by MCU

#### 2.18 MCD Serial I/F and NVM

Data of internal registers and non-volatile memory (NVM) can be configured via serial interface. When FG pin is Hi-Z, receiving serial commands is possible. IC enters serial mode after receiving the instruction code. In this mode, motor output stops, and FG pin is fixed to Hi-Z.

After inputting instruction code and following data (if needed), If ENB of Status Register is "0", IC returns to normal mode. If ENB of Status Register is "1", IC stays in serial mode.

#### 2.18.1 Serial commands

**Table 2-22 Serial commands (Instruction Code)**

| Command   | Code       | Description                            | Following Data                  |

|-----------|------------|----------------------------------------|---------------------------------|

| SR_READ   | 010 01 001 | Read status register                   | 8-bit data out                  |

| SR_WRITE  | 010 01 010 | Write status register                  | 8-bit data in                   |

| REG_READ  | 010 10 001 | Read normal register                   | 8-bit addr in + 16-bit data out |

| REG_WRITE | 010 10 010 | Write normal register                  | 8-bit addr in + 16-bit data in  |

| NVM_LOAD  | 010 11 001 | Load NVM data to normal register       | None                            |

| NVM_SAVE  | 010 11 010 | Store data of normal register to NVM   | None                            |

| NVM_ABORT | 010 11 100 | Terminate NVM writing process forcedly | None                            |

#### 2.18.2 Status register

Table 2-23 Status Register (SR)

| Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|---------|--------|-------|-------|-------|

| _     | _     |       | CAL_ERR | NVM_WR | WIRE  | ENB   | BUSY  |

| Name    | Description                       | Detail                                                                                                      |

|---------|-----------------------------------|-------------------------------------------------------------------------------------------------------------|

| BUSY    | State of register processing      | BUSY=0: Standby, BUSY=1: Under processing (REG_READ, REG_WRITE, NVM_LOAD, NVM_SAVE, NVM_COPY)               |

| ENB     | Serial command enable setting     | ENB=0: Normal mode (Only SR_READ SR_WRITE is acceptable.) ENB=1: Serial mode (All commands are acceptable.) |

| WIRE    | Serial communication mode setting | WIRE=0: 3-wire mode (SCK=SPD, SDI=FG, and SDO=ALERT) WIRE=1: 2-wire mode (SCK=SPD and SDIO=FG)              |

| NVM_WR  | NVM mode setting                  | NVM_WR=0: READ enable, WRITE disable<br>NVM_WR=1: READ disable, WRITE enable                                |

| CAL_ERR | Result of Hall position detection | CAL_ERR=0: Success CAL_ERR=1: Failure                                                                       |

### 2.18.3 Register map

#### Table 2-24 Register map

| 7:0   STARTDUTY [7:0]   Startup duty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ADDR | Bit             | Name              | Description                                                                                                      | Default |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|-------------------|------------------------------------------------------------------------------------------------------------------|---------|

| 14:8   STOPDUTY [6:0]   Stop duty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0    | 15:0            | USERID [15:0]     | -                                                                                                                | 0       |

| 7:0   STARTDUTY [7:0]   Startup duty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      | 15              | NOSTOP            | Non-stop mode (0: disable, 1: enable)                                                                            | 0       |

| 15:8   CHANGEDUTY [7:0]   Speed change point duty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1    | 14:8            | STOPDUTY [6:0]    | Stop duty                                                                                                        | 0       |

| 7:0   MAXDUTY [7:0]   Maximum duty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 7:0  | STARTDUTY [7:0] | Startup duty      | 0                                                                                                                |         |