MG32L003 User Guide

> Version 1.0 Date 2023/4/19

# **Contents**

| Co | onte | nts     |                                                            | 3  |

|----|------|---------|------------------------------------------------------------|----|

| ln | trod | uction  | 1                                                          | 1  |

| 1  | Doc  | cumer   | it convention                                              | 2  |

|    | 1.1  | The lis | st of abbreviations used in the register description table | 2  |

| 2  | Me   | mory :  | and bus architecture                                       | 3  |

| _  | 2.1  | _       | n structure                                                |    |

|    |      | -       | ge Address                                                 |    |

| 3  | Em   | bedde   | ed Flash (Flash)                                           | 6  |

|    | 3.1  |         | dded Flash Controller                                      |    |

|    | 3.2  | Funct   | ional description                                          | 6  |

|    |      | 3.2.1   | Erase operation                                            | 6  |

|    |      | 3.2.2   | Write operation                                            | 7  |

|    |      | 3.2.3   | Read operation                                             | 7  |

|    |      | 3.2.4   | Erasure time                                               | 7  |

|    |      | 3.2.5   | Write protection                                           | 7  |

|    |      | 3.2.6   | PC address erasure protection                              | 7  |

|    |      | 3.2.7   | Register write protection                                  | 8  |

|    | 3.3  | Syste   | m Boot Address Mapping                                     | 8  |

|    |      | 3.3.1   | Program boot                                               | 8  |

|    | 3.4  | Flash I | Registers                                                  | 9  |

|    | 3.5  | Flash I | Registers Description                                      | 9  |

|    |      | 3.5.1   | Flash control register(Flash_CR)                           | 9  |

|    |      | 3.5.2   | Flash Interrupt Flag Register(Flash_IFR)                   | 10 |

|    |      | 3.5.3   | Flash Interrupt Flag Clear Register(Flash_ICLR)            | 10 |

|    |      | 3.5.4   | Flash BYPASS Register(Flash_BYPASS)                        | 11 |

|    |      | 3.5.5   | Flash Sector erase protection register 0(Flash_SLOCK0)     | 11 |

|    |      | 3.5.6   | Flash Sector erase protection register 1(Flash_SLOCK1)     | 12 |

|    |      | 3.5.7   | Flash ISPCON Configuration Register(Flash_ISPCON)          | 14 |

| 4  | Сус  | lic Red | lundancy Check Unit(CRC)                                   | 15 |

|    | 4.1  | CRC in  | troduction                                                 | 15 |

|   | 4.2 | CRC f   | unctional description                                                             | 15 |

|---|-----|---------|-----------------------------------------------------------------------------------|----|

|   |     | 4.2.1   | CRC Encoding mode                                                                 | 15 |

|   |     | 4.2.2   | CRC Check mode                                                                    | 15 |

|   | 4.3 | CRC R   | egisters                                                                          | 16 |

|   | 4.4 | CRC R   | Registers Description                                                             | 16 |

|   |     | 4.4.1   | CRC Result Register(CRC_RESULT)                                                   | 16 |

|   |     | 4.4.2   | CRC Data Register((CRC_DATA)                                                      | 17 |

| 5 | Ope | erating | g Modes and Power Management                                                      | 18 |

|   | 5.1 |         | • Mode                                                                            |    |

|   | 5.2 |         | Mode                                                                              |    |

|   |     | 5.2.1   | How to enter sleep mode:                                                          | 19 |

|   |     |         |                                                                                   |    |

|   |     | 5.2.2   | How to exit sleep mode:                                                           | 19 |

|   |     | 5.2.3   | Note:                                                                             | 20 |

|   | 5.3 | Deep S  | Sleep Mode                                                                        | 20 |

|   |     | 5.3.1   | How to enter deep sleep mode :                                                    | 21 |

|   |     | 5.3.2   | How to exit deep sleep mode:                                                      | 21 |

|   | 5.4 | M0+ k   | Kernel system control register(SCR)                                               | 22 |

| 6 | Res | set an  | d Clock(RCC)                                                                      | 23 |

|   |     | Reset   |                                                                                   |    |

|   |     | 6.1.1   | Reset Controller Introduction                                                     | 23 |

|   |     |         | Reset source POR Reset                                                            |    |

|   | 6.2 |         | m clock                                                                           |    |

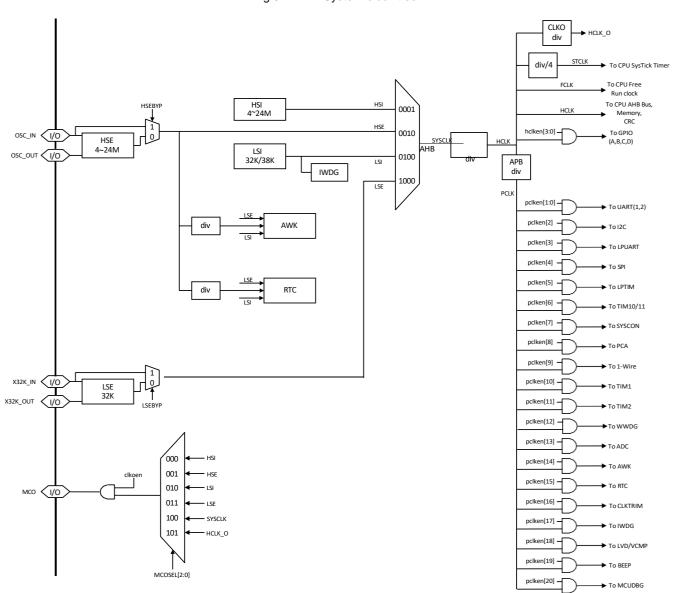

|   |     | 6.2.1   | System clock tree                                                                 | 25 |

|   |     | 6.2.2   | Internal High Speed RC Clock HSI                                                  | 25 |

|   |     | 6.2.3   | Internal Low Speed RC Clock LSI                                                   | 26 |

|   |     | 6.2.4   | External High Speed Crystal Clock HSE                                             | 26 |

|   |     | 6.2.5   | External Low Speed Crystal Clock LSE                                              | 26 |

|   |     | 6.2.6   | System clock startup process                                                      | 26 |

|   |     | 6.2.7   | System Clock Switching                                                            | 27 |

|   |     | 6.2.8   | The specific process of switching from internal high speed to external low speed  | 27 |

|   |     | 6.2.9   | The specific process of switching from internal high speed to external high speed | 27 |

|   |     | 6.2.10  | The specific process of switching from internal low speed to external high speed  | 27 |

|   |     | 6.2.11  | System clock output                                                               | 27 |

|   |     | 6.2.12  | 2 System Clock Security Control                                                   | 28 |

|   |      | 6.2.13 | IWDG Clock                                                            | 28 |

|---|------|--------|-----------------------------------------------------------------------|----|

|   |      | 6.2.14 | RTC Clock                                                             | 28 |

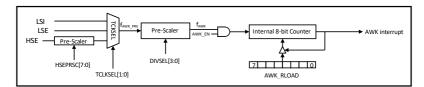

|   |      | 6.2.15 | AWK Clock                                                             | 28 |

|   |      | 6.2.16 | Low power consumption mode                                            | 28 |

|   | 6.3  | RCC R  | egisters                                                              | 29 |

|   | 6.4  | Regist | er Description                                                        | 29 |

|   |      | 6.4.1  | AHB Clock Frequency Division Register(RCC_HCLKDIV)                    | 29 |

|   |      | 6.4.2  | APB Clock Frequency Division Register(RCC_PCLKDIV)                    | 30 |

|   |      | 6.4.3  | AHB Peripheral module clock enable Register(RCC_HCLKEN)               | 30 |

|   |      | 6.4.4  | APB Peripheral module clock Enable register(RCC_PCLKEN)               | 31 |

|   |      | 6.4.5  | Clock output control register(RCC_MCOCR)                              | 32 |

|   |      | 6.4.6  | System reset control register(RCC_RSTCR)                              | 33 |

|   |      | 6.4.7  | System resets status register(RCC_RSTSR)                              | 33 |

|   |      | 6.4.8  | System Clock Source Configuration(RCC_SYSCLKCR)                       | 34 |

|   |      | 6.4.9  | System Clock Source Selection Register(RCC_SYSCLKSEL)                 | 35 |

|   |      | 6.4.10 | Internal High Speed RC Oscillator Control Register(RCC_HSICR)         | 36 |

|   |      | 6.4.11 | External high speed crystal oscillator control register(RCC_HSECR)    | 37 |

|   |      | 6.4.12 | Internal low speed RC oscillator control register(RCC_LSICR)          | 38 |

|   |      | 6.4.13 | External low speed crystal oscillator control register(RCC_LSECR)     | 38 |

|   |      |        | M0+ IRQ delay control register(RCC_IRQLATENCY)                        |    |

|   |      |        | SysTick Timer Register(RCC_STICKCR)                                   |    |

|   |      | 6.4.16 | SWDIO port control register(RCC_SWDIOCR)                              | 41 |

|   |      | 6.4.17 | Peripheral module resets the control register(RCC_PERIRST)            | 41 |

|   |      | 6.4.18 | RTC Reset control register(RCC_RTCRST)                                | 43 |

|   |      | 6.4.19 | Register Write protection control register(RCC_UNLOCK)                | 44 |

|   |      | 6.4.20 | Internal high speed RC oscillator control register 2(RCC_HSITC)       | 45 |

|   |      | 6.4.21 | Internal high speed RC oscillator control register 2(RCC_HSITC)       | 45 |

|   |      | 6.4.22 | Internal Low speed RC oscillator control register 2(RCC_LSITRIM)      | 46 |

| 7 | Syst | tem Co | ntrol(SYSCON)                                                         | 48 |

|   | 7.1  | SYS Re | gisters                                                               | 48 |

|   | 7.2  | Regist | er Description                                                        | 48 |

|   |      | 7.2.1  | System configuration register 0(SYSCON_CFGR0)                         | 48 |

|   |      | 7.2.2  | Terminal Deep Sleep Interrupt Mode Control Register(SYSCON_PORTINTCR) | 49 |

|   |      | 7.2.3  | Terminal control register(SYSCON_PORTCR)                              | 49 |

|   |      | 7.2.4  | PCA Capture channel control register(SYSCON_PCACR)                    | 52 |

|   |      | 7.2.5  | TIM1 channel input source selection(SYSCON_TIM1CR)                    | 53 |

|   |      | 7.2.6    | TIM2 channel input source selection(SYSCON_TIM2CR)                            | 57 |

|---|------|----------|-------------------------------------------------------------------------------|----|

|   |      | 7.2.7    | Syscon register write protection(SYSCON_UNLOCK)                               | 61 |

| 8 | Inte | errupt ( | Controller(NVIC)                                                              | 62 |

| _ | 8.1  |          | uction                                                                        |    |

|   | 8.2  |          | es                                                                            |    |

|   | 8.3  |          | pt priority                                                                   |    |

|   | 8.4  |          | pt vector table                                                               |    |

|   | 8.5  | Interru  | pt wake-up control WIC                                                        | 64 |

|   |      | 8.5.1    | NVIC wakes up from deep-sleep mode to interrupt ISR setting                   | 64 |

|   |      | 8.5.2    | NVIC wakes up from Deep Sleep mode setting and does not execute interrupt ISR | 64 |

|   |      | 8.5.3    | Use the exit sleep feature                                                    | 64 |

|   | 8.6  | Softwa   | are                                                                           | 65 |

|   |      | 8.6.1    | External interrupt enable                                                     | 65 |

|   |      | 8.6.2    | NVIC interrupt enable and clear enable                                        | 65 |

|   |      | 8.6.3    | NVIC interrupt pending and clear pending                                      | 65 |

|   |      | 8.6.4    | NVIC Interrupt Priority                                                       | 65 |

|   |      | 8.6.5    | NVIC interrupt mask                                                           | 66 |

|   | 8.7  | NVIC F   | Registers                                                                     | 67 |

|   | 8.8  | Regist   | er Description                                                                | 68 |

|   |      | 8.8.1    | Interrupt enable set register(NVIC_ISER)                                      | 68 |

|   |      | 8.8.2    | Interrupt enables clear register(NVIC_ICER)                                   | 68 |

|   |      | 8.8.3    | Interrupt suspends the setting register(NVIC_ISPR)                            | 69 |

|   |      | 8.8.4    | Interrupt suspends the clear register(NVIC_ICPR)                              | 69 |

|   |      | 8.8.5    | Interrupt priority control register 0(NVIC_IPR0)                              | 70 |

|   |      | 8.8.6    | Interrupt priority control register 1(NVIC_IPR1)                              | 70 |

|   |      | 8.8.7    | Interrupt priority control register 2(NVIC_IPR2)                              | 71 |

|   |      | 8.8.8    | Interrupt priority control register 3(NVIC_IPR3)                              | 71 |

|   |      | 8.8.9    | Interrupt priority control register 4(NVIC_IPR4)                              | 72 |

|   |      | 8.8.10   | Interrupt priority control register 5(NVIC_IPR5)                              | 72 |

|   |      | 8.8.11   | Interrupt priority control register 6(NVIC_IPR6)                              | 73 |

|   |      | 8.8.12   | Interrupt priority control register 7(NVIC_IPR7)                              | 73 |

| 9 | Ger  | neral p  | ourpose input and output(GPIO)                                                | 74 |

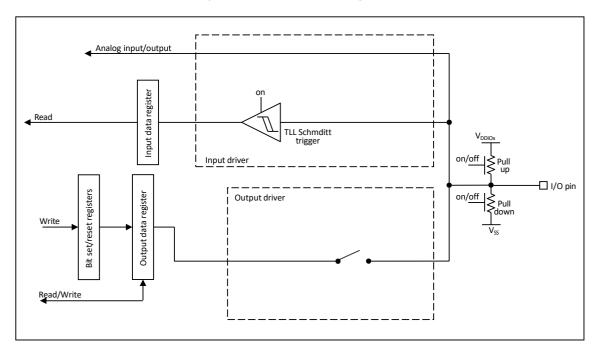

|   | 9.1  | GPIO     | Introduction                                                                  | 74 |

|   | 9.2  | GPIO     | main features                                                                 | 74 |

|   | 9.3  | GPIO     | Function description                                                          | 74 |

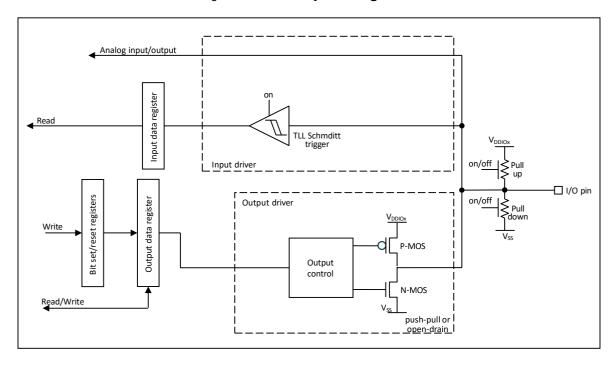

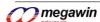

|   |      | 9.3.1    | General purpose I/O(GPIO)                                                     | 76 |

|        | 9.3.2  | I/O port control register                                                    | 77  |

|--------|--------|------------------------------------------------------------------------------|-----|

|        | 9.3.3  | I/O port data register                                                       | 77  |

|        | 9.3.4  | I/O data bit processing                                                      | 77  |

|        | 9.3.5  | Input configuration                                                          | 77  |

|        | 9.3.6  | Output configuration                                                         | 78  |

|        | 9.3.7  | External interrupt/wake up line                                              | 79  |

|        | 9.3.8  | I/O pin alternate function and remapping                                     | 79  |

|        | 9.3.9  | General input/output (GPIO)                                                  | 81  |

|        | 9.3.10 | Analog configuration                                                         | 82  |

|        | 9.3.11 | HSE or LSE pins are used as GPIO                                             | 83  |

| 9.4    | GPIO   | Registers                                                                    | 84  |

| 9.5    | GPIO   | Register Description                                                         | 85  |

|        | 9.5.1  | GPIO port direction register(GPIOx_DIRCR)(x = AD)                            | 85  |

|        | 9.5.2  | GPIO Port output type register(GPIOx_OTYPER)(x = AD)                         | 85  |

|        | 9.5.3  | GPIO Port output data register(GPIOx_ODR)(x = AD)                            | 86  |

|        | 9.5.4  | GPIO Port input data register(GPIOx_IDR)(x = AD)                             | 87  |

|        | 9.5.5  | GPIO Port interrupt enable register(GPIOx_INTEN)(x = AD)                     | 88  |

|        | 9.5.6  | GPIO Port interrupt original status register(GPIOx_RAWINTSR)(x = AD)         | 89  |

|        | 9.5.7  | GPIO Port interrupt status register(GPIOx_MSKINTSR)(x = AD)                  | 90  |

|        | 9.5.8  | GPIO Port interrupt clear register(GPIOx_INTCLR)(x = AD)                     | 91  |

|        | 9.5.9  | GPIO Port interrupt type register(GPIOx_INTTYPCR)(x = AD)                    | 92  |

|        | 9.5.10 | GPIO Interrupt type value register(GPIOx_INTPOLCR)(x = AD)                   | 93  |

|        | 9.5.11 | GPIO port arbitrary edge trigger interrupt register(GPIOx_INTANY)(x = AD)    | 94  |

|        | 9.5.12 | P GPIO Port output set register(GPIOx_ODSET)(x = AD)                         | 95  |

|        | 9.5.13 | B GPIO Port output clear register(GPIOx_ODCLR)(x = AD)                       | 96  |

|        | 9.5.14 | GPIO Port input dejitter register(GPIOx_INDBEN)(x = AD)                      | 97  |

|        | 9.5.15 | GPIO Port input dejitter clock configuration register(GPIOx_DBCLKCR)(x = AD) | 97  |

|        | 9.5.16 | GPIO Port pull-up/pull-down register(GPIOx_PUPDR)(x = AD)                    | 98  |

|        | 9.5.17 | GPIO Port voltage conversion rate configuration(GPIOx_SLEWCR)(x = AD)        | 100 |

|        | 9.5.18 | GPIO Port drive intensity configuration register(GPIOx_DRVCR)(x = AD)        | 101 |

|        | 9.5.19 | GPIO Port alternate function register(GPIOx_AFR)(x = AD)                     | 102 |

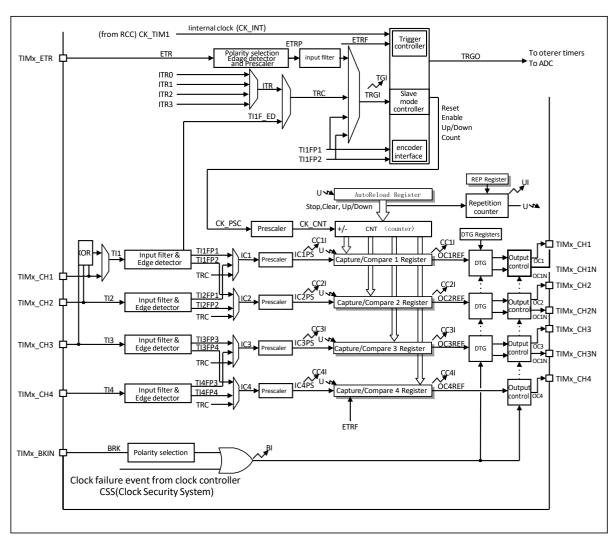

| IO Adv | vance  | d-control timers(TIM1)                                                       | 117 |

| 10.1   | I TIM1 | introduction                                                                 | 117 |

|        | 10.1.1 | TIM1 main features                                                           | 117 |

|        | 10.1.2 | 2 TIM1 functional description                                                | 118 |

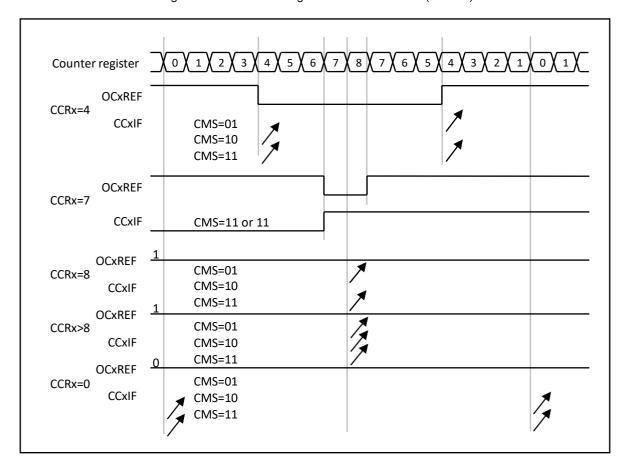

|        | 10.1.3 | Counter modes                                                                | 120 |

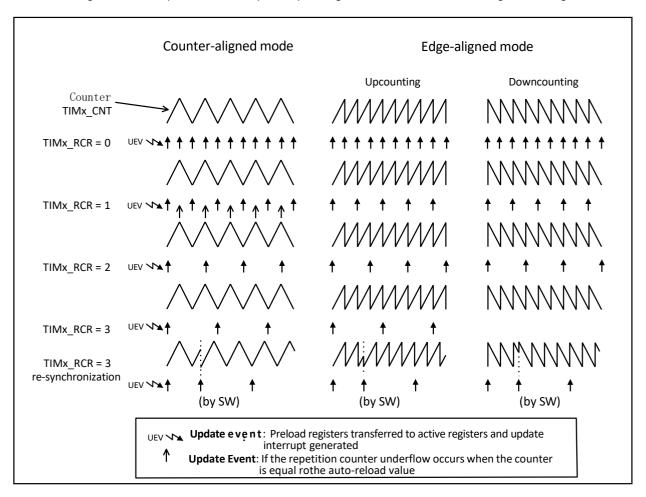

|     | 10.1.4 F   | Repetition counter                               | 129 |

|-----|------------|--------------------------------------------------|-----|

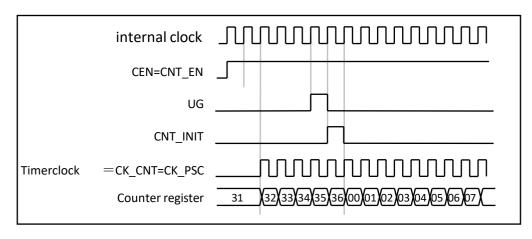

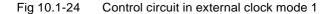

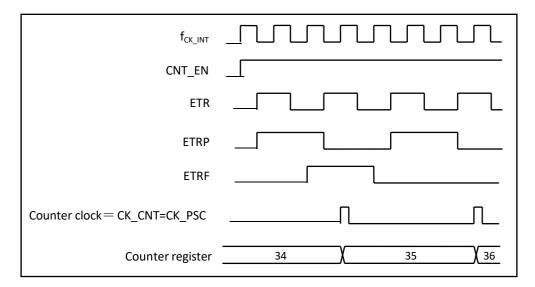

|     | 10.1.5     | Clock selection                                  | 130 |

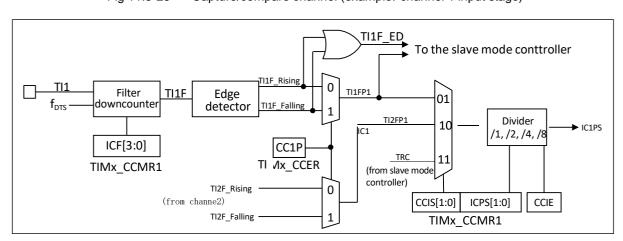

|     | 10.1.6     | Capture/compare channels                         | 133 |

|     | 10.1.7 l   | nput capture mode                                | 135 |

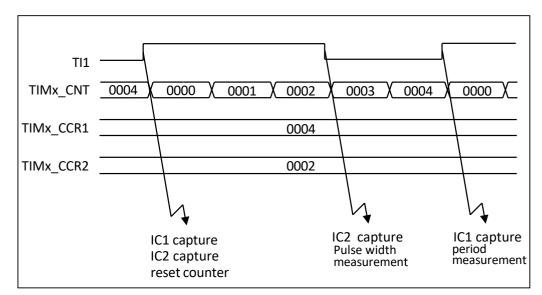

|     | 10.1.8 F   | PWM input mode                                   | 136 |

|     | 10.1.9 F   | Forced output mode                               | 137 |

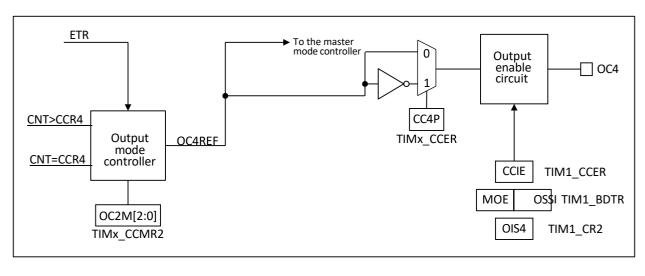

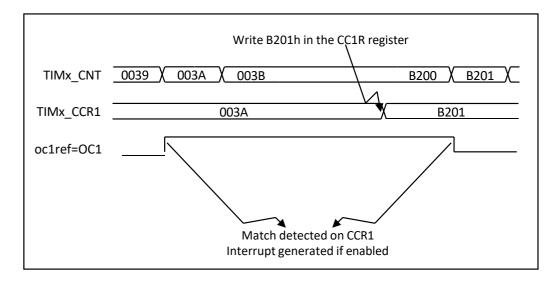

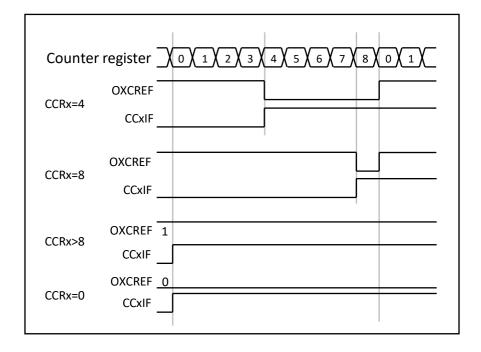

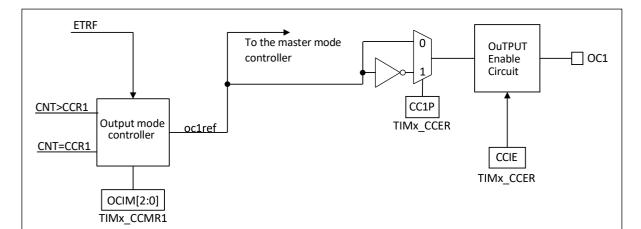

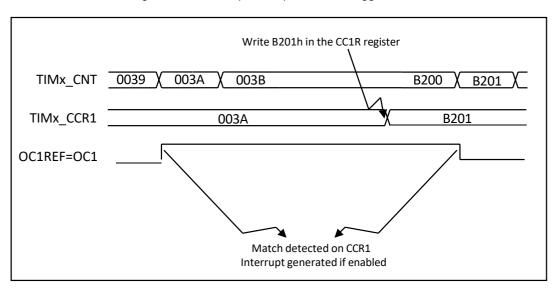

|     | 10.1.10    | Output compare mode                              | 137 |

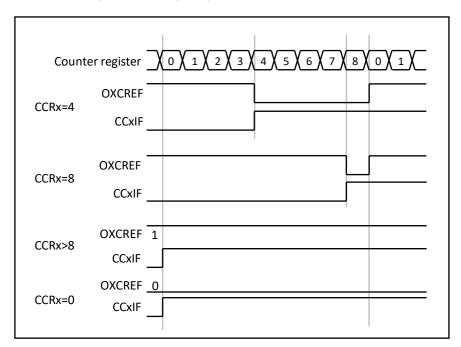

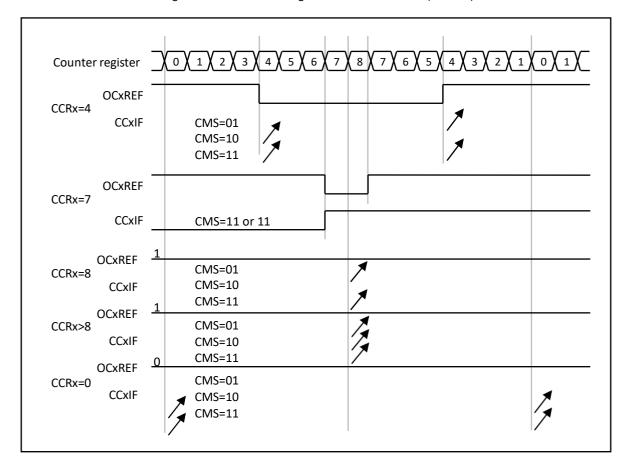

|     | 10.1.11    | PWM mode                                         | 138 |

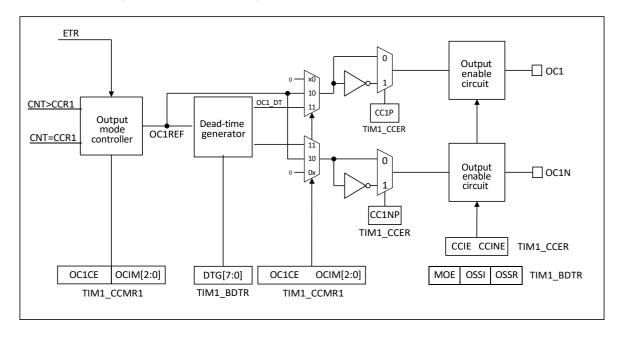

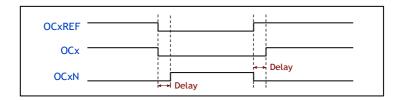

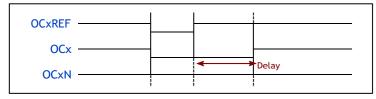

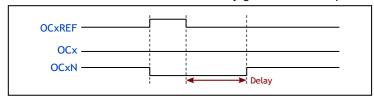

|     | 10.1.12    | Complementary outputs and dead-time insertion    | 141 |

|     | 10.1.13    | Re-directing OCxREF to OCx or OCxN               | 142 |

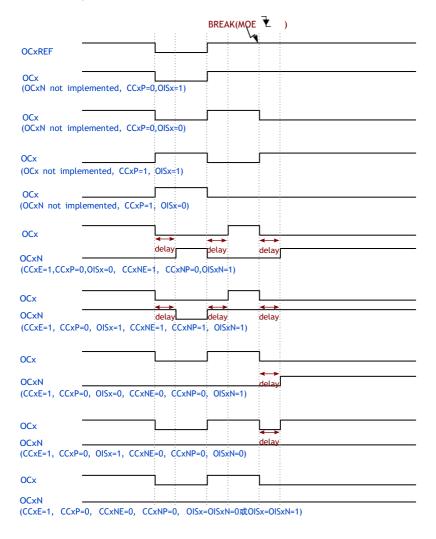

|     | 10.1.14    | Using the break function                         | 142 |

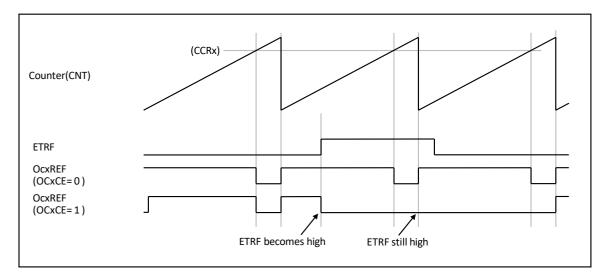

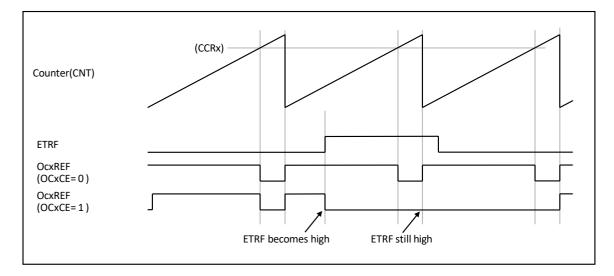

|     | 10.1.15    | Clearing the OCxREF signal on an external event  | 144 |

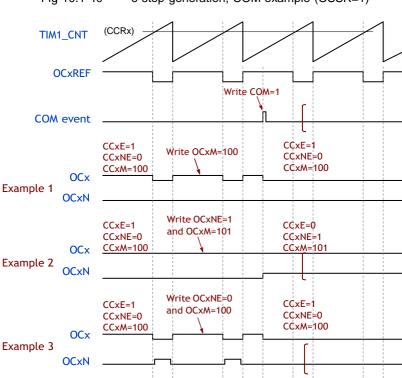

|     | 10.1.16    | 6-step PWM generation                            | 145 |

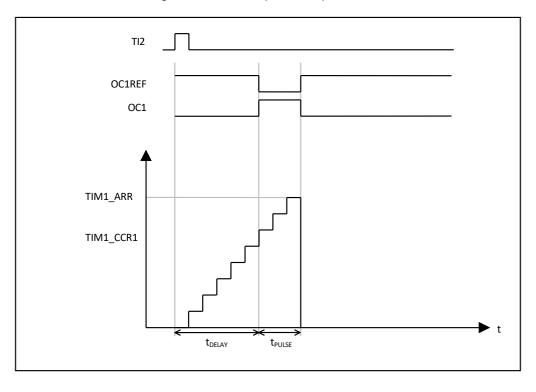

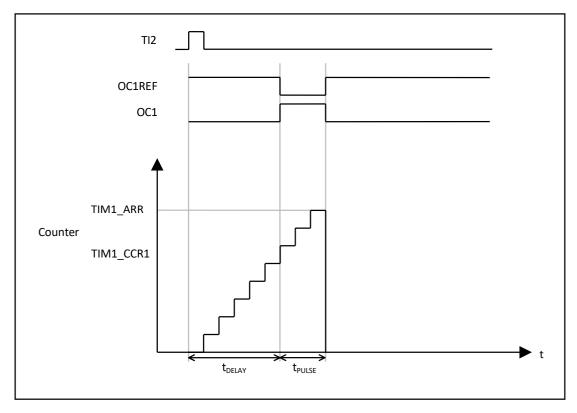

|     | 10.1.17    | One-pulse mode                                   | 146 |

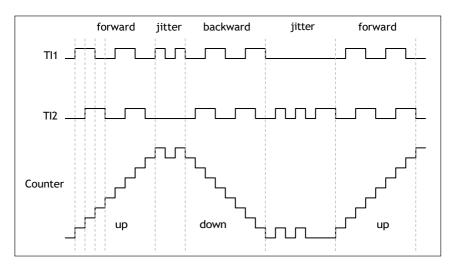

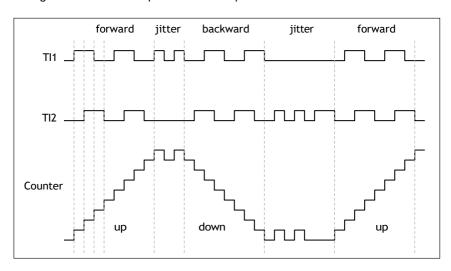

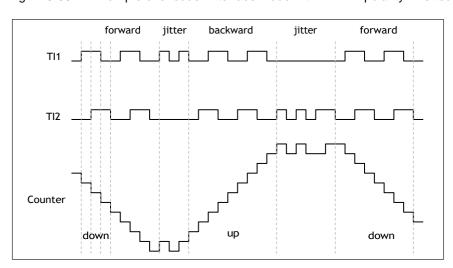

|     | 10.1.18    | Encoder interface mode                           | 148 |

|     | 10.1.19    | Timer input XOR function                         | 150 |

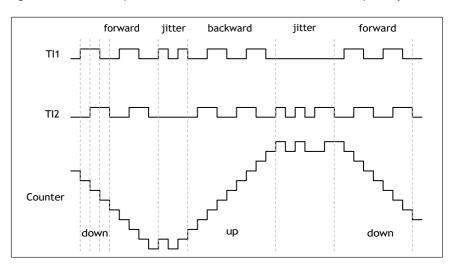

|     | 10.1.20    | Interfacing with Hall sensors                    | 150 |

|     | 10.1.21    | TIM1 and external trigger synchronization        | 152 |

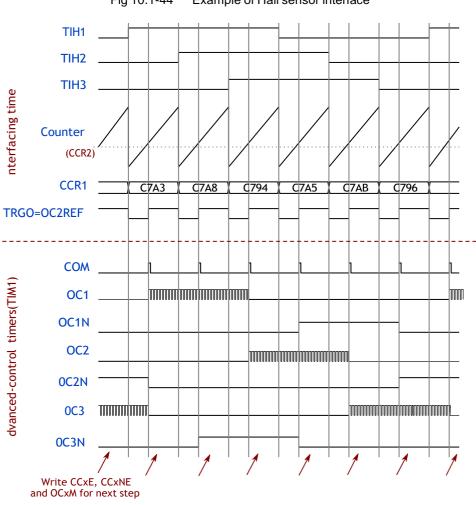

|     | 10.1.22    | Slave mode: Reset mode                           | 152 |

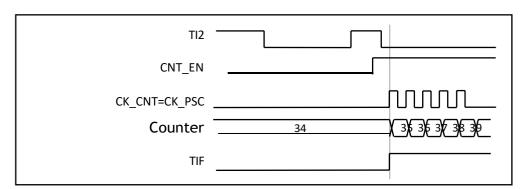

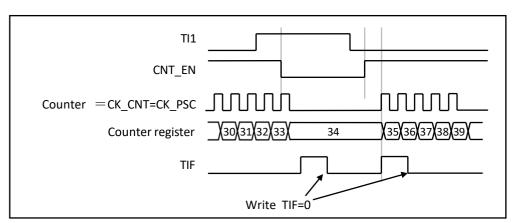

|     | 10.1.23    | Slave mode: Gated mode                           | 153 |

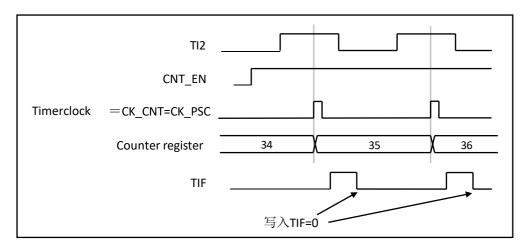

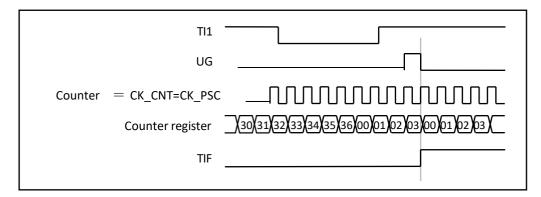

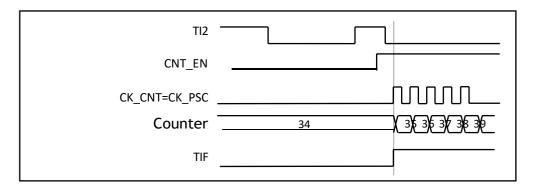

|     | 10.1.24    | Slave mode: Trigger mode                         | 154 |

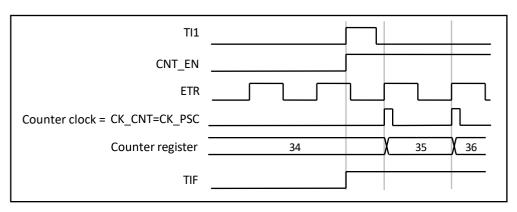

|     | 10.1.25    | Slave mode: external clock mode 2 + trigger mode | 155 |

|     | 10.1.26    | Timer synchronization                            | 155 |

|     | 10.1.27    | Debug mode                                       | 156 |

| 10. | .2 TIM1 Re | egisters                                         | 156 |

| 10. | .3 TIM1 re | gister description                               | 157 |

|     | 10.3.1 T   | FIM1 control register 1(TIM1_CR1)                | 157 |

|     | 10.3.2 T   | FIM1 control register 2(TIM1_CR2)                | 158 |

|     | 10.3.3 T   | TIM1 slave mode control register(TIM1_SMCR)      | 161 |

|     | 10.3.4 T   | TIM1 interrupt enable register(TIM1_DIER)        | 163 |

|     | 10.3.5 T   | TIM1 status register (TIM1_SR)                   | 164 |

|     | 10.3.6 T   | TIM1 event generation register(TIM1_EGR)         | 167 |

|     | 10.3.7 T   | TIM1 capture/compare mode register 1(TIM1_CCMR1) | 168 |

|     | 10.3.8 T   | TIM1 capture/compare mode register 2(TIM1_CCMR2) | 171 |

|     | 10.3.9 T   | FIM1_CCMR2 capture/compare mode register 2       | 172 |

|     | 10.3.10    | TIM1 capture/compare enable register(TIM1_CCER)  | 174 |

|     | 10.3.11    | TIM1 counter(TIM1_CNT)                           | 176 |

| 10.3.12       | TIM1 prescaler(TIM1_PSC)                                  | 177 |

|---------------|-----------------------------------------------------------|-----|

| 10.3.13       | TIM1 auto-reload register(TIM1_ARR)                       | 177 |

| 10.3.14       | TIM1 repetition counter register (TIM1_RCR)               | 178 |

| 10.3.15       | TIM1 capture/compare register 1(TIM1_CCR1)                | 179 |

| 10.3.16       | TIM1 capture/compare register2(TIM1_CCR2)                 | 179 |

| 10.3.17       | TIM1 capture/compare register 3 (TIM1_CCR3)               | 180 |

| 10.3.18       | TIM1 capture/compare register 4(TIM1_CCR4)                | 180 |

| 10.3.19       | TIM1 break and dead-time register(TIM1_BDTR)              | 182 |

| 11 General-pu | rpose(TIM2)                                               | 185 |

| _             | roduction                                                 |     |

| 11.2 TIM2 ma  | ain features                                              | 185 |

| 11.3 TIM2 fur | nctional description                                      | 186 |

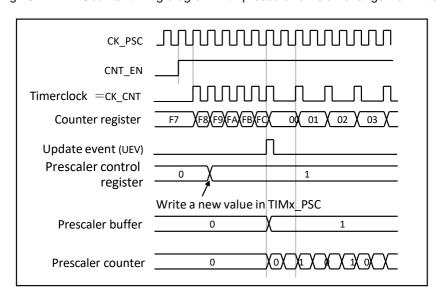

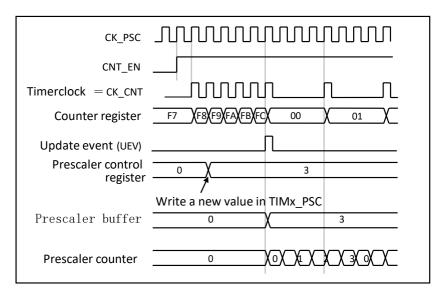

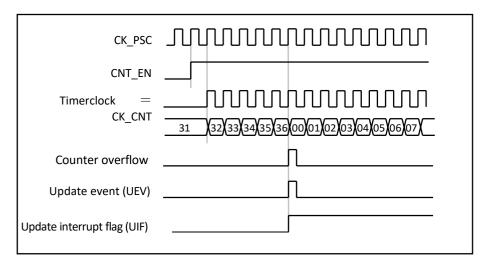

| 11.3.1 T      | ime-base unit                                             | 186 |

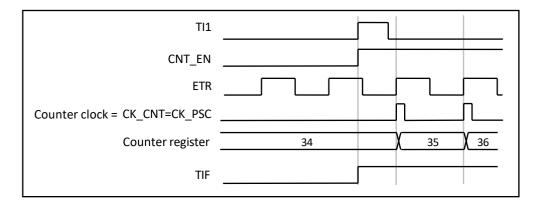

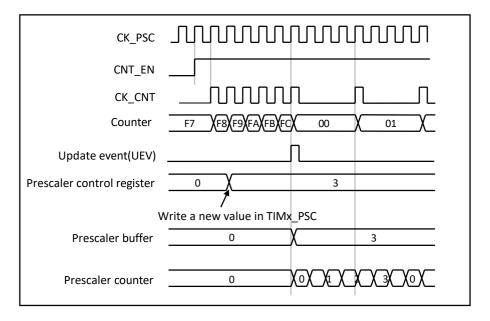

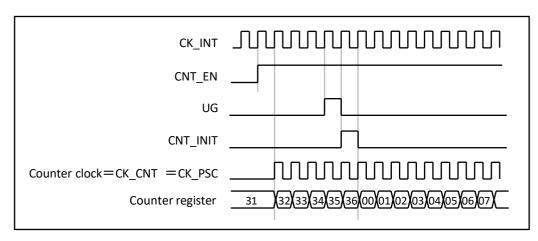

| 11.3.2 F      | Prescaler description                                     | 186 |

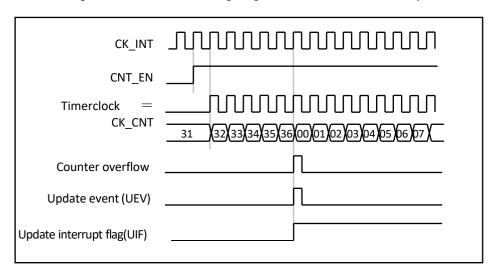

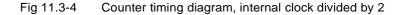

| 11.3.3 C      | Counter modes                                             | 187 |

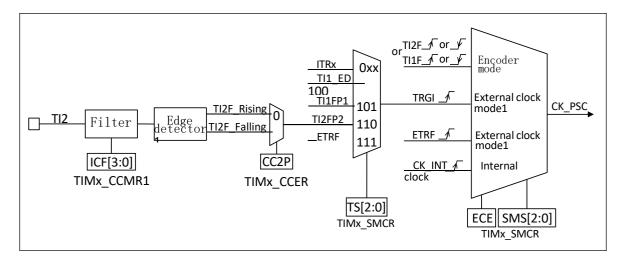

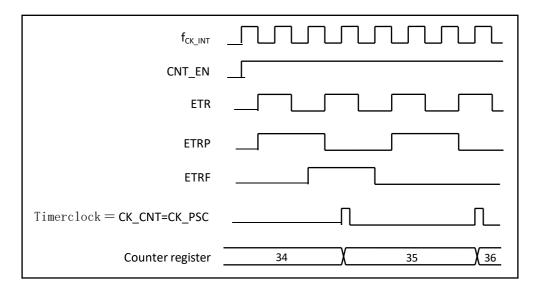

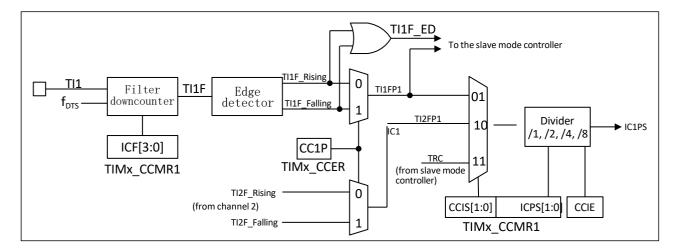

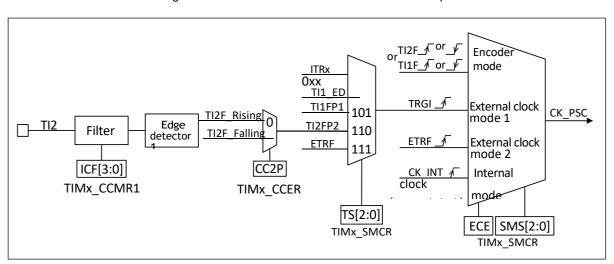

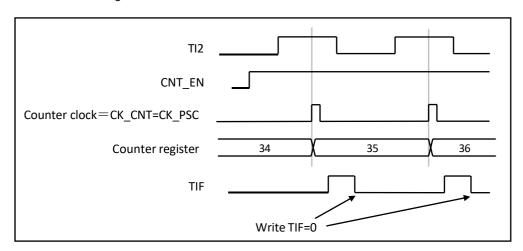

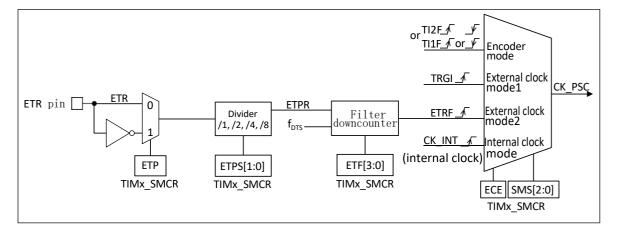

| 11.3.4 C      | Clock selection                                           | 195 |

| 11.3.5 F      | PWM input mode                                            | 200 |

| 11.3.6 F      | Forced output mode                                        | 201 |

| 11.3.7 (      | Output compare mode                                       | 202 |

| 11.3.8 F      | PWM mode                                                  | 203 |

| 11.3.9 C      | One-pulse mode                                            | 206 |

| 11.3.10       | Particular case: OCx fast enable:                         | 207 |

| 11.3.11       | Clearing the OCxREF signal on an external event:          | 207 |

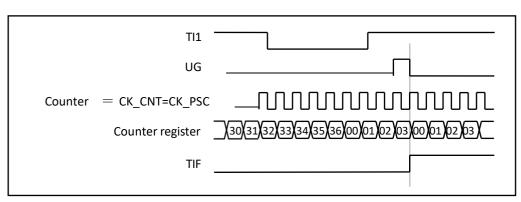

| 11.3.12       | Encoder interface mode                                    | 208 |

| 11.3.13       | Timer input XOR function                                  | 210 |

| 11.3.14       | Timer and external trigger synchronization                | 211 |

| 11.3.15       | Slave mode: Reset mode                                    | 211 |

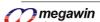

| 11.3.16       | Slave mode: Gated mode                                    | 211 |

| 11.3.17       | Slave mode: Trigger mode                                  | 212 |

| 11.3.18       | Slave mode: external clock mode 2 + trigger mode          | 213 |

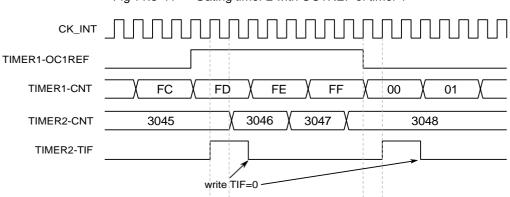

| 11.3.19       | Master/Slave timer example                                | 214 |

| 11.3.20       | Using one timer as prescaler for another timer            | 214 |

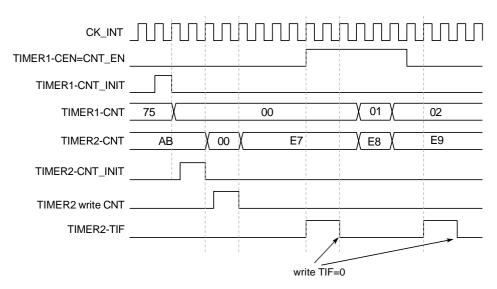

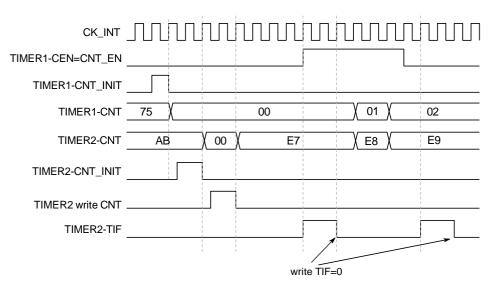

| 11.3.21       | Using one timer to enable another timer                   | 215 |

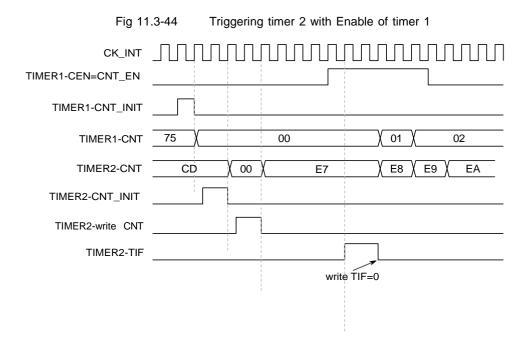

| 11.3.22       | Using one timer to start another timer                    | 216 |

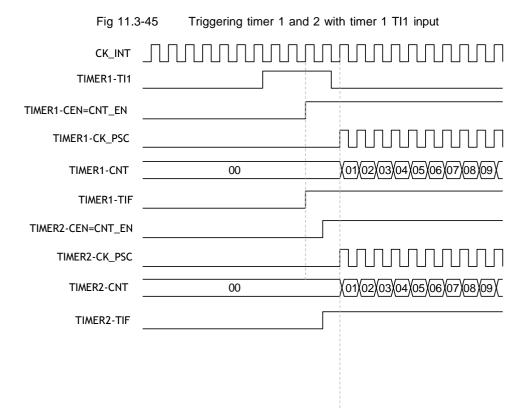

| 11.3.23       | 2 timers synchronously in response to an external trigger | 217 |

| 11 2 24       | Dehug mode                                                | 219 |

|   | 11.4 TIM2 Register                                                                                                                                                                                                                                                                                                                                             | ∠18               |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|   | 11.5 TIM2 Register Description                                                                                                                                                                                                                                                                                                                                 | 220               |

|   | 11.5.1 TIM2 control register 1(TIM2_CR1)                                                                                                                                                                                                                                                                                                                       | 220               |

|   | 11.5.2 TIM2 control register 2(TIM2_CR2)                                                                                                                                                                                                                                                                                                                       | 222               |

|   | 11.5.3 TIM2 slave mode control register(TIM2_SMCR)                                                                                                                                                                                                                                                                                                             | 224               |

|   | 11.5.4 TIM2 interrupt enable register(TIM2_DIER)                                                                                                                                                                                                                                                                                                               | 227               |

|   | 11.5.5 TIM2 status register(TIM2_SR)                                                                                                                                                                                                                                                                                                                           | 228               |

|   | 11.5.6 TIM2 event generation register(TIM2_EGR)                                                                                                                                                                                                                                                                                                                | 230               |

|   | 11.5.7 TIM2 capture/compare mode register 1 (TIM2_CCMR1)                                                                                                                                                                                                                                                                                                       | 231               |

|   | 11.5.8 TIM2 capture/compare mode register 2(TIM2_CCMR2)                                                                                                                                                                                                                                                                                                        | 234               |

|   | 11.5.9 TIM2 capture/compare enable register(TIM2_CCER)                                                                                                                                                                                                                                                                                                         | 236               |

|   | 11.5.10 TIM2 counter(TIM2_CNT)                                                                                                                                                                                                                                                                                                                                 | 238               |

|   | 11.5.11 TIM2 prescaler(TIM2_PSC)                                                                                                                                                                                                                                                                                                                               | 238               |

|   | 11.5.12 TIM2 auto-reload register(TIM2_ARR)                                                                                                                                                                                                                                                                                                                    | 239               |

|   | 11.5.13 TIM2 capture/compare register 1(TIM2_CCR1)                                                                                                                                                                                                                                                                                                             | 239               |

|   | 11.5.14 TIM2 capture/compare register 2(TIM2_CCR2)                                                                                                                                                                                                                                                                                                             | 239               |

|   | 11.5.15 TIM2 capture/compare register 3(TIM2_CCR3)                                                                                                                                                                                                                                                                                                             | 240               |

|   | 11.5.16 TIM2 capture/compare register 4(TIM2_CCR4)                                                                                                                                                                                                                                                                                                             | 240               |

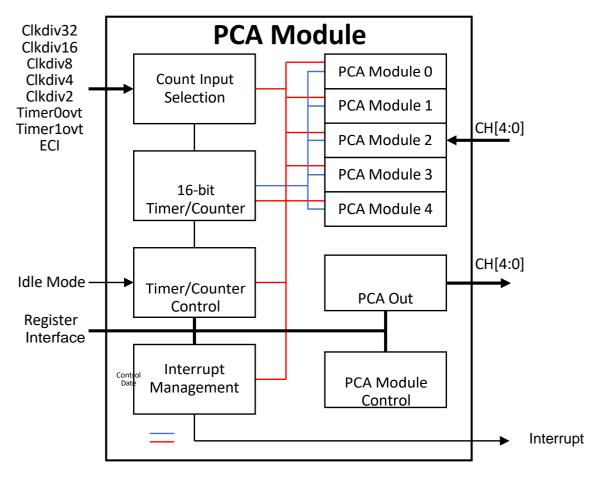

| 1 | 12 Programmable Counter Array(PCA)                                                                                                                                                                                                                                                                                                                             | 242               |

|   | 12.1 PCA introduction                                                                                                                                                                                                                                                                                                                                          |                   |

|   | 12.2 PCA functional description                                                                                                                                                                                                                                                                                                                                | 243               |

|   |                                                                                                                                                                                                                                                                                                                                                                |                   |

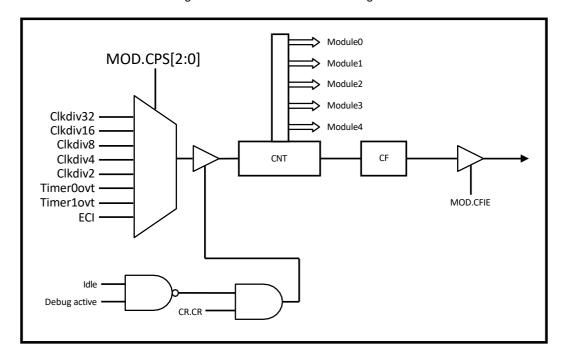

|   | 12.2.1 PCA Timer/Counter                                                                                                                                                                                                                                                                                                                                       | 243               |

|   |                                                                                                                                                                                                                                                                                                                                                                |                   |

|   | 12.2.1 PCA Timer/Counter                                                                                                                                                                                                                                                                                                                                       | 245               |

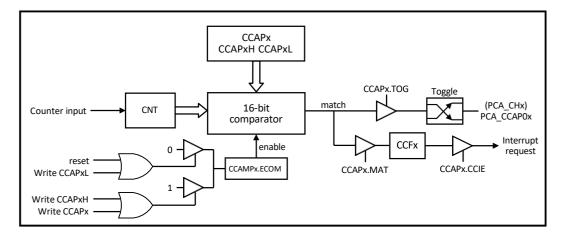

|   | 12.2.2 Capture function                                                                                                                                                                                                                                                                                                                                        | 245<br>246        |

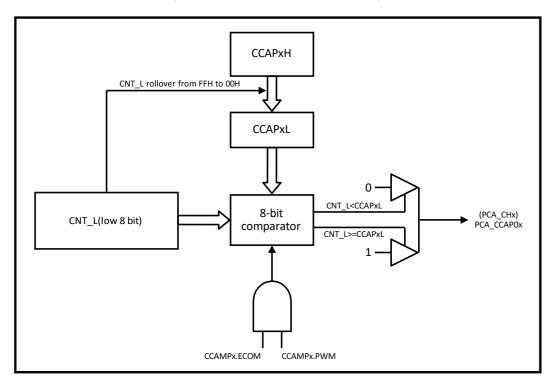

|   | 12.2.2 Capture function                                                                                                                                                                                                                                                                                                                                        | 245<br>246<br>249 |

|   | 12.2.2 Capture function                                                                                                                                                                                                                                                                                                                                        | 245<br>246<br>249 |

|   | 12.2.2 Capture function                                                                                                                                                                                                                                                                                                                                        |                   |

|   | 12.2.2 Capture function  12.2.3 PCA comparison function  12.3 PCA Module interconnection and control with other modules  12.3.1 ECI Interconnection  12.3.2 PCACAP0  12.3.3 PCACAP1/2/3/4  12.4 PCA registers  12.5 PCA registers description                                                                                                                  |                   |

|   | 12.2.2 Capture function  12.2.3 PCA comparison function.  12.3 PCA Module interconnection and control with other modules.  12.3.1 ECl Interconnection.  12.3.2 PCACAP0.  12.3.3 PCACAP1/2/3/4.  12.4 PCA registers  12.5 PCA registers description.  12.5.1 PCA control register (PCA_CR)                                                                      |                   |

|   | 12.2.2 Capture function                                                                                                                                                                                                                                                                                                                                        |                   |

|   | 12.2.2 Capture function  12.2.3 PCA comparison function  12.3 PCA Module interconnection and control with other modules  12.3.1 ECl Interconnection  12.3.2 PCACAP0  12.3.3 PCACAP1/2/3/4  12.4 PCA registers  12.5 PCA registers description  12.5.1 PCA control register (PCA_CR)  12.5.2 PCA mode register (PCA_MOD)  12.5.3 PCA counter register (PCA_CNT) |                   |

| 12.5.7 8 LSB bits register of PCA capture/compare (PCA_CCAP0~4L) | 256 |

|------------------------------------------------------------------|-----|

| 12.5.8 Compare Capture 16 Bit Register (PCA_CCAP0~4)             | 257 |

| 12.5.9 Compare High Speed Output Flag Register (PCA_CCAPO)       | 257 |

| 12.5.10 PCA Port output control register (PCA_POCR)              | 258 |

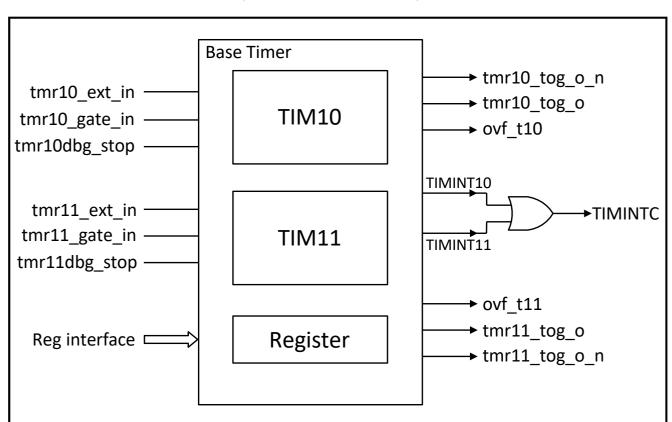

| 13 Base timer(TIM10/TIM11)                                       | 260 |

| 13.1 Base Timer introduction                                     | 260 |

| 13.2 Base Timer description                                      | 260 |

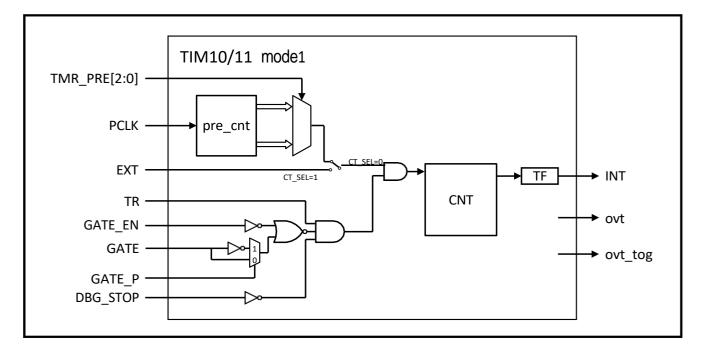

| 13.2.1 Mode 1 free counting                                      | 261 |

| 13.2.2 Mode 2 reload                                             | 261 |

| 13.2.3 Counting function                                         | 262 |

| 13.2.4 Timing function                                           | 263 |

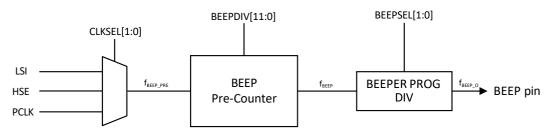

| 13.2.5 Buzzer Features                                           | 264 |

| 13.3 Base Timer interconnection                                  | 264 |

| 13.3.1 GATE Interconnection                                      | 264 |

| 13.3.2 Toggle Output Interconnection                             | 265 |

| 13.4 Base Timer registers                                        | 265 |

| 13.5 Base Timer registers description                            | 265 |

| 13.5.1 Control Register(TIMx_CR)                                 | 265 |

| 13.5.2 Immediate Reload Register(TIMx_LOAD)                      | 266 |

| 13.5.3 Counter Register(TIMx_CNT)                                | 267 |

| 13.5.4 Raw interrupt status register(TIMx_RAWINTSR)              | 267 |

| 13.5.5 Interrupt flag register(TIMx_MSKINTSR)                    | 267 |

| 13.5.6 Interrupt clear register(TIMx_INTCLR)                     | 268 |

| 13.5.7 BackGround Cycle reload register(TIMx_BGLOAD)             | 268 |

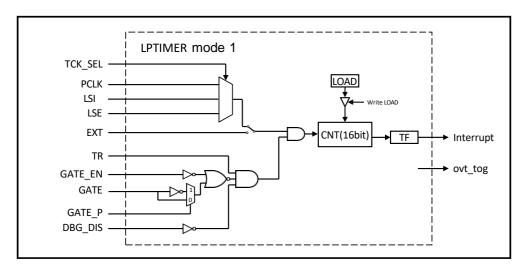

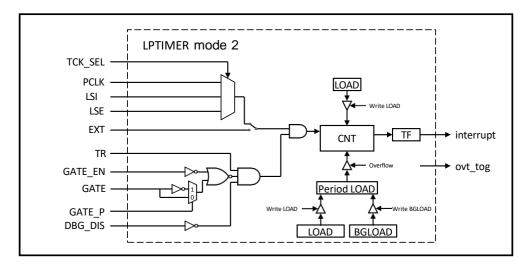

| 14 Low Power Timer(LPTIM)                                        | 270 |

| 14.1 LPTIM description                                           | 270 |

| 14.1.1 Counting function                                         | 272 |

| 14.1.2 Timing function                                           | 272 |

| 14.2 LPTIM Interconnection                                       | 272 |

| 14.2.1 GATE Interconnection                                      | 272 |

| 14.2.2 EXT Interconnection                                       | 272 |

| 14.2.3 TOGGLE Output Interconnection                             | 272 |

| 14.3 LPTIM Registers                                             | 272 |

| 14.4 LPTIM Registers description                                 | 273 |

| 14.4.1 LPTIM Count Value read-only Register (LPTIM_CNTVAL)       | 273 |

| 14.4.2 LPTIM Control Register (LPTIM_CR)                         | 273 |

| 14.4.3 LPTIM Immediate reload register(LPTIM_LOAD)    | 274 |

|-------------------------------------------------------|-----|

| 14.4.4 LPTIM Interrupt Register(LPTIM_INTSR)          | 275 |

| 14.4.5 LPTIM Interrupt Clear Register(LPTIM_INTCLR)   | 275 |

| 14.4.6 LPTIM Cycle reload register(LPTIM_BGLOAD)      | 275 |

| 15 Auto-wake-up Timer                                 | 277 |

| 15.1 AWK Registers                                    | 277 |

| 15.2 Register Description                             | 277 |

| 15.2.1 AWK timer control register(AWK_CR)             | 277 |

| 15.2.2 AWK timer reload data register(AWK_RLOAD)      | 278 |

| 15.2.3 AWK timer state register(AWK_SR)               | 279 |

| 15.2.4 AWK timer Interrupt Clear register(AWK_INTCLR) | 279 |

| 16 BEEP                                               | 280 |

| 16.1 BEEP introduction                                | 280 |

| 16.2 BEEP Functional description                      | 280 |

| 16.2.1 Buzzer operation                               | 280 |

| 16.2.2 Buzzer Calibration                             | 280 |

| 16.3 BEEP Registers                                   | 280 |

| 16.4 Registers description                            | 281 |

| 16.4.1 BEEP control register(BEEP_CSR)                | 281 |

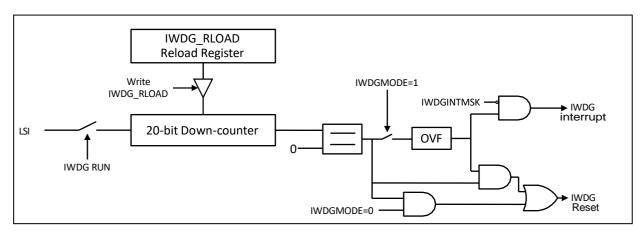

| 17 Independent watchdog (IWDG)                        | 282 |

| 17.1 IWDG introduction                                | 282 |

| 17.2 IWDG functional description                      | 282 |

| 17.2.1 Timeout period                                 | 282 |

| 17.2.2 IWDG Interrupt after overflow                  | 283 |

| 17.2.3 IWDG reset after overflow                      | 283 |

| 17.3 IWDG registers                                   | 283 |

| 17.4 Registers description                            | 284 |

| 17.4.1 IWDG Control Command Register (IWDG_CMDCR)     | 284 |

| 17.4.2 IWDG Configuration Register (IWDG_CFGR)        | 284 |

| 17.4.3 IWDG Counter Reload Register(IWDG_RLOAD)       | 285 |

| 17.4.4 IWDG Counter Value Register(IWDG_CNTVAL)       | 285 |

| 17.4.5 IWDG Interrupt Status Register(IWDG_SR)        | 286 |

| 17.4.6 IWDG Interrupt Clear register(IWDG_INTCLR)     | 286 |

| 17.4.7 IWDG protection register(IWDG_UNLOCK)          | 287 |

| 18 Window watchdog (WWDG)                             | 288 |

|     | 18.1 WWDG introduction                            | 288 |

|-----|---------------------------------------------------|-----|

|     | 18.2 WWDG main features                           | 288 |

|     | 18.3 WWDG BLOCK Diagram                           | 288 |

|     | 18.4 WWDG Basic configuration                     | 288 |

|     | 18.5 WWDG functional description                  | 289 |

|     | 18.5.1 WWDG counts                                | 289 |

|     | 18.5.2 WWDG comparison interrupt                  | 290 |

|     | 18.5.3 WWDG reset system                          | 290 |

|     | 18.5.4 Window setting limit of WWDG               | 290 |

|     | 18.6 WWDG compare with IWDG                       | 290 |

|     | 18.6.1 Reset Conditions and Reset Delays          | 290 |

|     | 18.6.2 Wake-up function                           | 290 |

|     | 18.7 WWDG Registers                               | 290 |

|     | 18.8 Register description                         | 291 |

|     | 18.8.1 WWDG Reload Count Register(WWDG_RLOAD)     | 291 |

|     | 18.8.2 WWDG Control Register (WWDG_CR)            | 291 |

|     | 18.8.3 WWDG Interrupt Enable Register(WWDG_INTEN) | 292 |

|     | 18.8.4 WWDG Status Register (WWDG_SR)             | 292 |

|     | 18.8.5 WWDG Interrupt Clear Register(WWDG_INTCLR) | 293 |

|     | 18.8.6 WWDG Counter Value Register(WWDG_CNTVAL)   | 293 |

|     |                                                   | 005 |

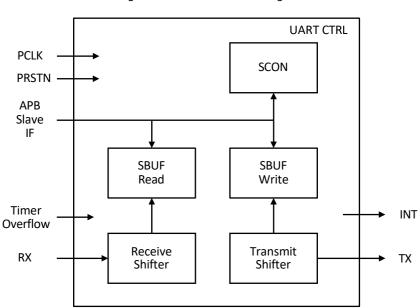

| 1 % | 19 UART1/UART2                                    |     |

|     | 19.1 UART introduction                            |     |

|     | 19.2 UART Block Diagram                           |     |

|     | 19.3 UART Operating Modes                         |     |

|     | 19.3.1 Mode 0(synchronous mode, half duplex)      |     |

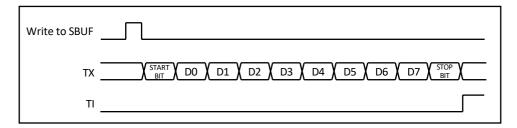

|     | 19.3.2 Mode 1(asynchronous mode, full duplex)     |     |

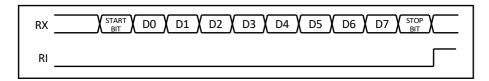

|     | 19.3.3 Mode 2(asynchronous mode, full duplex)     |     |

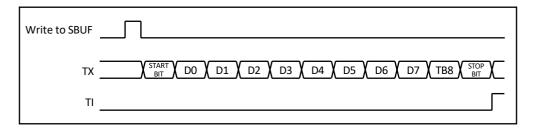

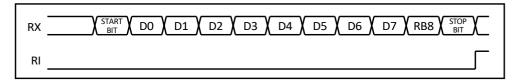

|     | 19.3.4 Mode 3(asynchronous mode, full duplex)     |     |

|     | 19.3.5 Baud rate programming                      |     |

|     | 19.3.6 Frame error detection                      |     |

|     | 19.3.7 Multi-machine communication                | 299 |

|     |                                                   |     |

|     | 19.3.8 Automatic Address Recognition              |     |

|     | 19.3.9 Given address                              | 300 |

|     | 19.3.9 Given address                              | 300 |

|     | 19.3.9 Given address                              | 300 |

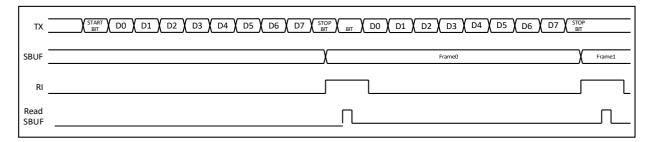

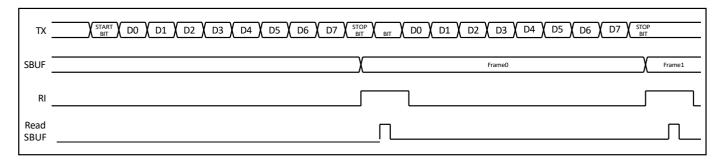

| 19.4.2 Transmitter                                | 30               |

|---------------------------------------------------|------------------|

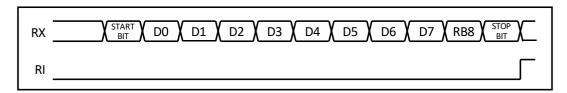

| 19.4.3 Receiver                                   | 30               |

| 19.5 Different baud rate frequency division Setti | ngs30            |

| 19.6 UART Registers                               | 30               |

| 19.7 Register Description                         | 30               |

| 19.7.1 UART Control Register(UART_SCC             | DN)              |

| 19.7.2 UART Data Register(UARTx_SBUF              | ·)30             |

| 19.7.3 UART Address Register(UARTx_S/             | ADDR)30          |

| 19.7.4 UART Address Mask Register(UAR             | Tx_SADEN)30      |

| 19.7.5 UART Interrupt Flag Register(UAR)          | _INTSR)309       |

| 19.7.6 UART Interrupt Flag Clear Register         | (UART_INTCLR)309 |

| 19.7.7 UART Baud Rate Control Register(           | JART_BAUDCR)310  |

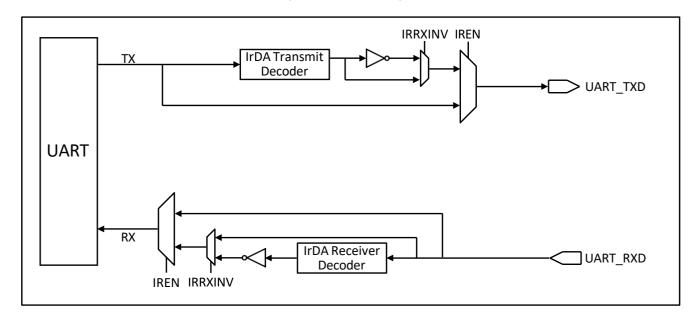

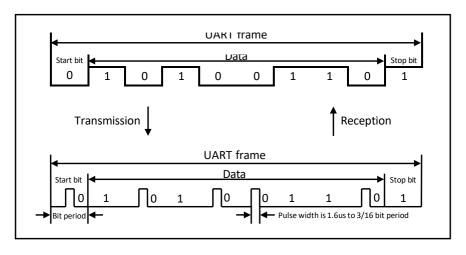

| 19.7.8 UART IrDA Control Register(UART            | _IRDACR)310      |

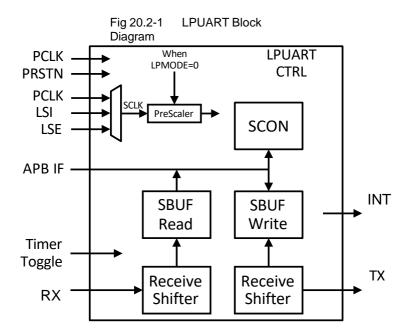

| 20 LPUART                                         | 312              |

| 20.1 LPUART Introduction                          | 31               |

| 20.2 LPUART Diagram                               | 31               |

| 20.3 Operating Modes                              | 31               |

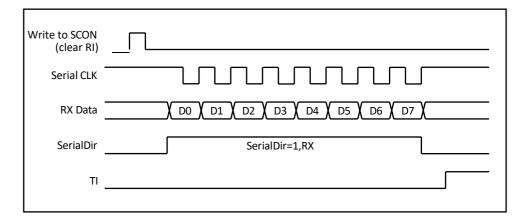

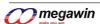

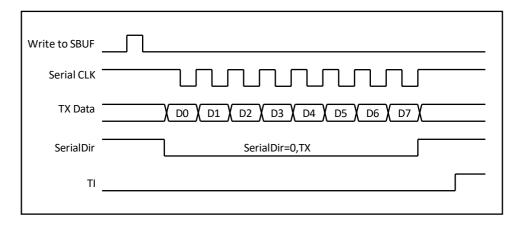

| 20.3.1 Mode 0(synchronous mode, half du           | plex)            |

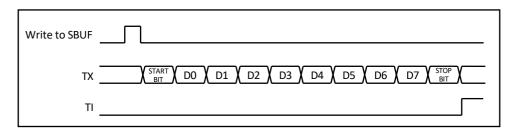

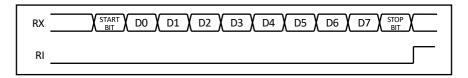

| 20.3.2 Mode 1(asynchronous mode, full du          | ıplex)           |

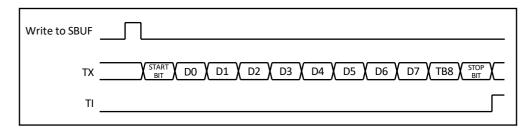

| 20.3.3 Mode 2(asynchronous mode, full du          | ıplex)           |

| 20.3.4 Mode 3(asynchronous mode, full du          | ıplex)           |

| 20.4 Baud rate programming                        | 310              |

| 20.4.1 Mode 0                                     | 310              |

| 20.4.2 Mode 1/3                                   | 310              |

| 20.4.3 Mode 2                                     | 31               |

| 20.5 Frame error detection                        | 31               |

| 20.6 Multi-machine communication                  | 31               |

| 20.7 Automatic Address Recognition                | 31               |

| 20.8 Given address                                | 31               |

| 20.9 Broadcast addresses                          | 31               |

| 20.9.1 Examples of given address and bro          | adcast address31 |

| 20.10 Transceiver buffer                          | 31               |

| 20.10.1 Receive buffer                            | 31               |

| 20.10.2 Send buffer                               | 31               |

| 20.11 Registers                                   | 31               |

| 20.12 Register Description                        | 31               |

| 20.12.1         | LPUART Data Register(LPUART_SBUF)                   | 319 |

|-----------------|-----------------------------------------------------|-----|

| 20.12.2         | LPUART Control Register(LPUART_SCON)                | 320 |

| 20.12.3         | LPUART Address Register(LPUART_SADDR)               | 321 |

| 20.12.4         | LPUART Address Mask Register(LPUART_SADEN)          | 322 |

| 20.12.5         | LPUART Interrupt Flag Register(LPUART_INTSR)        | 322 |

| 20.12.6         | LPUART Interrupt Flag Clear Register(LPUART_INTCLR) | 323 |

| 20.12.7         | LPUART Baud Rate Control Register(LPUART_BAUDCR)    | 323 |

| 21 I2C Interfa  | ce                                                  | 325 |

|                 | oduction                                            |     |

|                 | n features                                          |     |

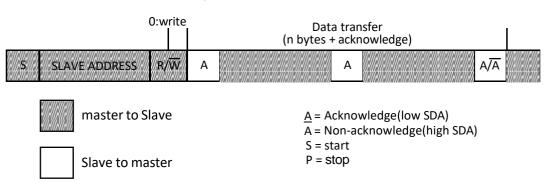

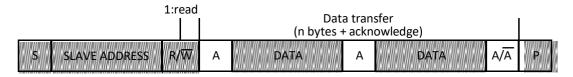

|                 | tocol description                                   |     |

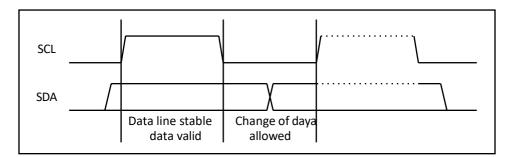

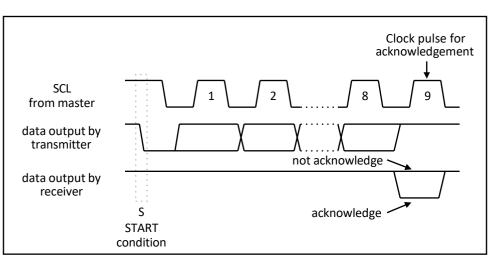

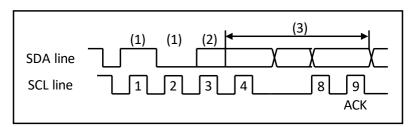

|                 | Data transfer on the I2C bus                        |     |

| 21.3.2 \$       | Start bit or Repeated start signal                  | 326 |

|                 | Slave Address Transfer                              |     |

| 21.3.4 [        | Oata transmission                                   | 327 |

| 21.4 I2C des    | cription                                            | 328 |

| 21.5 I2C Ope    | erating mode                                        | 329 |

| 21.5.1 A        | Arbitration and Synchronization Logic               | 330 |

|                 | serial clock generator                              |     |

| 21.5.3 li       | nput filter                                         | 331 |

| 21.5.4 <i>A</i> | Address comparator                                  | 331 |

| 21.5.5 li       | nterrupt generator                                  | 331 |

| 21.5.6 l        | 2C Master Transmit Mode                             | 331 |

| 21.5.7 1        | 2C Master Receive Mode                              | 335 |

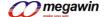

| 21.5.8 1        | 2C Slave Receive Mode                               | 338 |

| 21.5.9 1        | 2C Slave Transmitter Mode                           | 342 |

| 21.5.10         | I2C Miscellaneous Status                            | 344 |

| 21.5.11         | I2C_SR = 0xF8                                       | 345 |

| 21.5.12         | I2C_SR = 0x00                                       | 345 |

| 21.6 Operatir   | ng mode                                             | 345 |

| 21.6.1 iı       | nitializer                                          | 345 |

| 21.6.2 F        | Port configuration program                          | 345 |

| 21.6.3 \$       | Start the master sending function                   | 345 |

| 21.6.4 \$       | Start the master receiving function                 | 346 |

| 21.6.5 1        | 2C Interrupt Routine                                | 346 |

| 21.6.6 r        | no mode specified                                   | 346 |

| 21.6.7 Master sending status                                    | 347 |

|-----------------------------------------------------------------|-----|

| 21.6.8 Master Receive Status                                    | 347 |

| 21.6.9 Slave receiving state                                    | 348 |

| 21.6.10 Slave sending status                                    | 350 |

| 21.7 I2C Registers                                              | 351 |

| 21.8 I2C Register description                                   | 351 |

| 21.8.1 I2C Configuration Register(I2C_CR)                       | 351 |

| 21.8.2 I2C Data Register(I2C_DATA)                              | 352 |

| 21.8.3 I2C Address Register(I2C_ADDR)                           | 352 |

| 21.8.4 I2C Status Register(I2C_SR)                              | 352 |

| 21.8.5 I2C Baud Rate Counter Enable(I2C_TIMRUN)                 | 353 |

| 21.8.6 I2C Baud Rate Counter Configuration Register(I2C_BAUDCR) | 353 |

| 22 Serial peripheral interface(SPI)                             | 355 |

| 22.1 SPI introduction                                           | 355 |

| 22.2 SPI main features                                          | 355 |

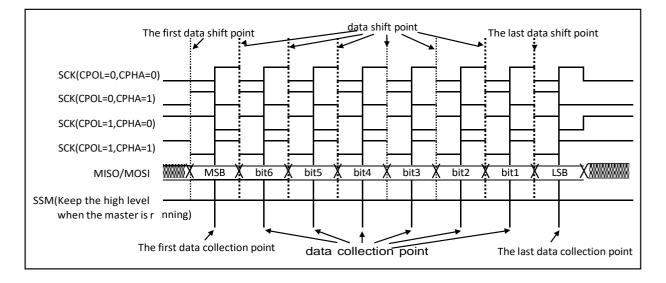

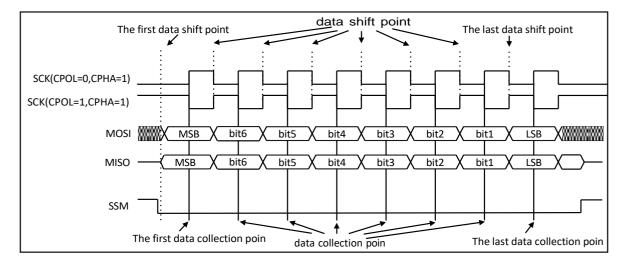

| 22.3 SPI functional description                                 | 355 |

| 22.3.1 SPI master mode                                          | 355 |

| 22.3.2 SPI slave mode                                           | 356 |

| 22.4 SPI interrupts                                             | 358 |

| 22.5 Multi-Master/Multi-Slave Mode                              | 358 |

| 22.6 SPI Registers                                              | 360 |

| 22.7 SPI register description                                   | 360 |

| 22.7.1 SPI control register(SPI_CR)                             | 360 |

| 22.7.2 SPI slice selection configuration register (SPI_SSN)     | 361 |

| 22.7.3 SPI state register (SPI_SR)                              | 361 |

| 22.7.4 SPI data register (SPI_DATA)                             | 362 |

| 23 One-Wire Interface (OWIRE)                                   | 363 |

| 23.1 One-Wire Protocol(One-Wire)                                | 363 |

| 23.1.1 Features                                                 | 363 |

| 23.1.2 Advantage                                                | 363 |

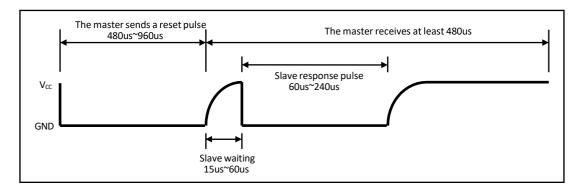

| 23.2 Single bus communication process                           | 363 |

| 23.2.1 Initialization                                           | 363 |

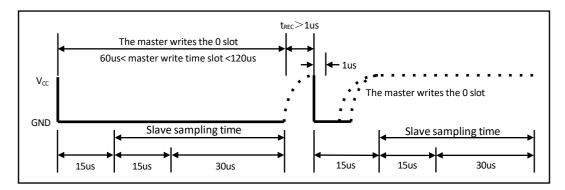

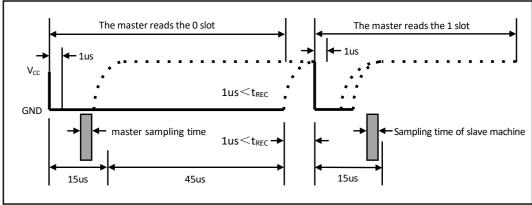

| 23.2.2 Write gap                                                | 363 |

| 23.2.3 Read gap                                                 | 364 |

| 23.3 Configuration description                                  | 364 |

| 23.3.1 Initial configuration instructions                       | 364 |

| megawin megawin                                                 |     |

|      | 23.3.2 Write data configuration instructions                                     | 365 |

|------|----------------------------------------------------------------------------------|-----|

| 2    | 23.4 Registers                                                                   | 366 |

| 2    | 3.5 Registers description                                                        | 366 |

|      | 23.5.1 One-Wire Module Control Register(OWIRE_CR)                                | 366 |

|      | 23.5.2 One-Wire Input terminal filter control register(OWIRE_NFCR)               | 368 |

|      | 23.5.3 One-Wire RESET Control Register(OWIRE_RSTCNT)                             | 369 |

|      | 23.5.4 One-Wire Presence PuLXT counter register(OWIRE_PRESCNT)                   | 370 |

|      | 23.5.5 One-Wire Bit rate Design counter(OWIRE_BITRATECNT)                        | 371 |

|      | 23.5.6 One-Wire Master device Read/write time of PULL0 drive (OWIRE_DRVCNT)      | 372 |

|      | 23.5.7 One-Wire Master device read sampling time setting (OWIRE_RDSMPCNT)        | 373 |

|      | 23.5.8 One-Wire Recover Time Counting interval value (OWIRE_RECCNT)              | 374 |

|      | 23.5.9 One-Wire Data Register (OWIRE_DATA)                                       | 375 |

|      | 23.5.10 One-Wire Bus operation command register (OWIRE_CMD)                      | 376 |

|      | 23.5.11 One-Wire Interrupt enable (OWIRE_INTEN)                                  | 377 |

|      | 23.5.12 One-Wire status register(OWIRE_SR)                                       | 378 |

|      | 23.5.13 One-Wire Status clear register(OWIRE_INTCLR)                             | 379 |

| 24 C | Clock Trim/Monitoring module(CLKTRIM)                                            | 380 |

|      | 24.1 CLKTRIM introduction                                                        |     |

|      | 24.2 CLKTRIM main features                                                       |     |

|      | 4.3 CLKTRIM functional description                                               |     |

| _    | 24.3.1 CLKTRIM calibration mode                                                  |     |

|      | 24.3.2 CLKTRIM monitoring mode                                                   |     |

| 2    | 24.4 CLKTRIM registers                                                           |     |

|      | 4.5 CLKTRIM registers description                                                |     |

| _    | 24.5.1 Configuration Register(CLKTRIM_CR)                                        |     |

|      | 24.5.2 Reference Counter Disposition Configuration Register(CLKTRIM_REFCON)      |     |

|      | 24.5.3 Reference Counter Value Register(CLKTRIM_REFCNT)                          |     |

|      | 24.5.4 Calibration Counter Value Register(CLKTRIM_CALCNT)                        |     |

|      | 24.5.5 Interrupt Flag Register(CLKTRIM_IFR)                                      |     |

|      | 24.5.6 Interrupt Flag Clear Register(CLKTRIM_ICLR)                               |     |

|      | 24.5.7 Calibration Counter Overflow Value Configuration Register(CLKTRIM_CALCON) |     |

|      |                                                                                  |     |

|      | Real-time clock (RTC)                                                            |     |

|      | 25.1 RTC introduction                                                            |     |

|      | 25.2 RTC main features                                                           |     |

| 2    | 25.3 RTC functional description                                                  |     |

|      | 25.3.1 RTC block diagram                                                         | 386 |

|        | 25.3.2 RTC clock                                       | . 387 |

|--------|--------------------------------------------------------|-------|

|        | 25.3.3 Reset process                                   | . 387 |

|        | 25.3.4 Register write protection                       | . 387 |

|        | 25.3.5 Calendar initialization and configuration       | . 388 |

|        | 25.3.6 Read count register                             | . 388 |

|        | 25.3.7 Write count register                            | . 389 |

|        | 25.3.8 Alarm clock setting                             | . 389 |

|        | 25.3.9 Calibrated 1Hz output                           | . 389 |

|        | 25.3.10 RTC clock calibration                          | . 389 |

| 25.4   | RTC interrupt                                          | . 390 |

|        | 25.4.1 RTC alarm interrupt                             | . 390 |

|        | 25.4.2 RTC cycle interrupt                             | . 390 |

| 25.5   | RTC Registers                                          | . 391 |

| 25.6   | RTC Registers Description                              | . 392 |

|        | 25.6.1 RTC Control Register(RTC_CR)                    | . 392 |

|        | 25.6.2 RTC Clock Control Register(RTC_CLKCR)           | . 393 |

|        | 25.6.3 RTC Time Register(RTC_TIME)                     | . 394 |

|        | 25.6.4 RTC Date Register (RTC_DATE)                    | . 394 |

|        | 25.6.5 RTC Time Alarm Register(RTC_ALM1TIME)           | . 395 |

|        | 25.6.6 RTC Date Alarm Register (RTC_ALM1DATE)          | . 396 |

|        | 25.6.7 RTC Periodic Alarm Clock Register (RTC_ALM2PRD) | . 397 |

|        | 25.6.8 RTC Clock Trim Register (RTC_CLKTRIM)           | . 397 |

|        | 25.6.9 RTC Initialize and Status Registers (RTC_ISR)   | . 398 |

|        | 25.6.10 RTC Status Clear Register(RTC_INTCLR)          | . 399 |

|        | 25.6.11 RTC Write Protection Register(RTC_WPR)         | . 400 |

| 26 Ana | alog-to-digital converter (ADC)                        | 401   |

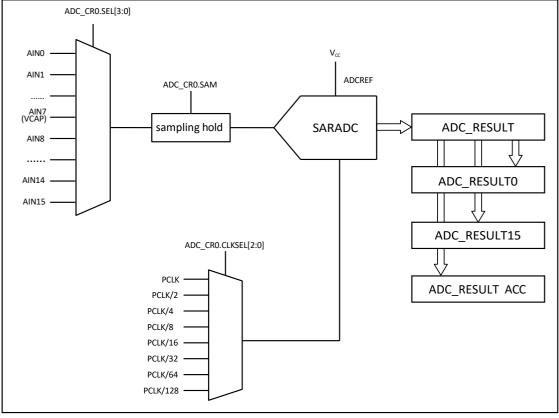

| 26.1   | ADC introduction                                       | . 401 |

| 26.2   | ADC Block Diagram                                      | . 401 |

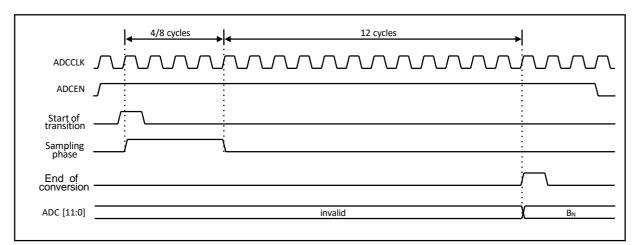

| 26.3   | Conversion timing and speed                            | . 402 |

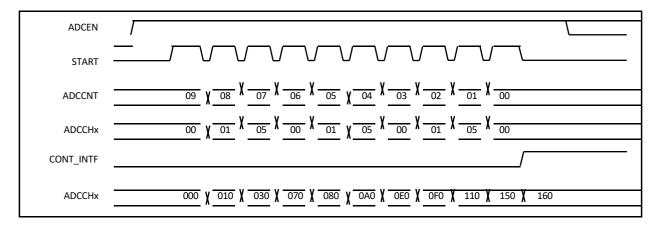

| 26.4   | Single Conversion Mode                                 | . 402 |

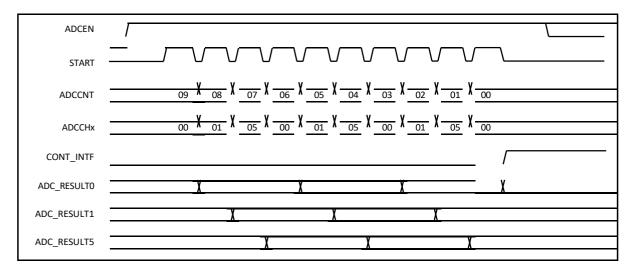

| 26.5   | Continuous Conversion Mode                             | . 403 |

|        | Continuous transformation cumulative mode              |       |

|        | Comparison of ADC conversion results                   |       |

|        | ADC interrupt                                          |       |

| 26.9   | ADC Register                                           | . 407 |

|        | 26.9.1 ADC Configuration Register(ADC_CR0)             | . 408 |

|      | 26.9.2 A        | ADC Configuration Register 1((ADC_CR1)                   | 410 |

|------|-----------------|----------------------------------------------------------|-----|

|      | 26.9.3 A        | ADC Configuration Register 2(ADC_CR2)                    | 416 |

|      | 26.9.4 A        | ADC channel 0 conversion result(ADC_RESULT0)             | 418 |

|      | 26.9.5 A        | ADC channel 1 conversion result(ADC_RESULT1)             | 418 |

|      | 26.9.6 A        | ADC channel 2 conversion result(ADC_RESULT2)             | 419 |

|      | 26.9.7 A        | ADC channel 3 conversion result(ADC_RESULT3)             | 419 |

|      | 26.9.8 A        | ADC channel 4 conversion result(ADC_RESULT4)             | 419 |

|      | 26.9.9 A        | ADC channel 5 conversion result(ADC_RESULT5)             | 421 |

|      | 26.9.10         | ADC channel 6 conversion result(ADC_RESULT6)             | 421 |

|      | 26.9.11         | ADC channel 7 conversion result(ADC_RESULT7)             | 423 |

|      | 26.9.12         | ADC conversion result(ADC_RESULT)                        | 423 |

|      | 26.9.13         | ADC Conversion result accumulation value(ADC_RESULT_ACC) | 423 |

|      | 26.9.14         | ADC comparison high threshold register(ADC_HT)           | 425 |

|      | 26.9.15         | ADC comparison low threshold register(ADC_LT)            | 425 |

|      | 26.9.16         | ADC Interrupt enable register(ADC_INTEN)                 | 426 |

|      | 26.9.17         | ADC interrupt clear register(ADC_INTCLR)                 | 427 |

|      | 26.9.18         | ADC Pre-mask interrupt status register(ADC_RAWINTSR)     | 429 |

|      | 26.9.19         | ADC Post-mask interrupt status register(ADC_MSKINTSR)    | 430 |

|      | 26.9.20         | ADC channel 8 conversion result(ADC_RESULT8)             | 432 |

|      | 26.9.21         | ADC channel 9 conversion result(ADC_RESULT9)             | 433 |

|      | 26.9.22         | ADC channel 10 conversion result(ADC_RESULT10)           | 433 |

|      | 26.9.23         | ADC channel 11 conversion result(ADC_RESULT11)           | 434 |

|      | 26.9.24         | ADC channel 12 conversion result(ADC_RESULT12)           | 434 |

|      | 26.9.25         | ADC channel 13 conversion result(ADC_RESULT13)           | 434 |

|      | 26.9.26         | ADC channel 14 conversion result(ADC_RESULT14)           | 435 |

|      | 26.9.27         | ADC channel 15 conversion result(ADC_RESULT15)           | 435 |

| 27 L | ow Voltag       | je Detector (LVD)                                        | 437 |

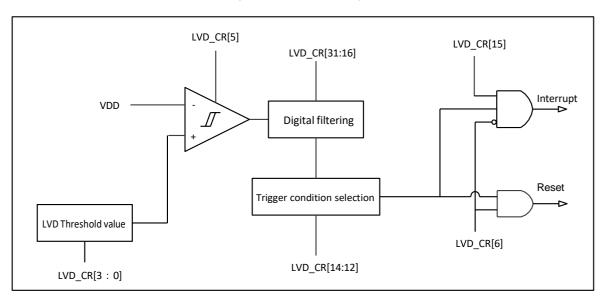

| 27   | 7.1 LVD intr    | oduction                                                 | 437 |

| 27   | 7.2 LVD Blo     | ck Diagram                                               | 437 |

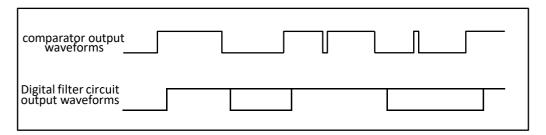

| 27   | 7.3 Digital fil | Itering                                                  | 437 |

| 27   | 7.4 Configur    | ration example                                           | 438 |

|      | 27.4.1 L        | VD configured as low voltage reset                       | 438 |

|      | 27.4.2 L        | VD configured as voltage change interrupt                | 438 |

| 27   | 7.5 LVD Re      | gisters                                                  | 439 |

| 27   | 7.6 LVD Re      | gisters Description                                      | 439 |

|      | 27 6 1 1        | \/D Control Register(L\/D_CR)                            | 130 |

| 27.6.2 LVD Status Registe         | r(LVD_SR)                         | 440 |

|-----------------------------------|-----------------------------------|-----|

| 28 Voltage Comparator(VCMI        | P)                                | 442 |

| 28.1 VCMP introduction            |                                   | 442 |

| 28.2 VCMP Block Diagram           |                                   | 442 |

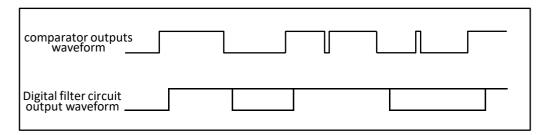

| 28.3 Digital Filtering            |                                   | 442 |

|                                   |                                   |     |

|                                   |                                   |     |

| 28.6 VCMP Registers Description   | on                                | 443 |

| 28.6.1 Voltage comparator         | control register(VCMP_CR0)        | 443 |

| 28.6.2 Voltage comparator         | control register(VCMP_CR1)        | 444 |

| 28.6.3 VCMP Output Confi          | iguration Register(VCMP_OUTCFG)   | 445 |

| 28.6.4 VCMP Status Regis          | ster(VCMP_SR)                     | 447 |

| 29 Option Bytes                   |                                   | 448 |

| 29.1 Introduction                 |                                   | 448 |

| 29.2 Registers                    |                                   | 448 |

| 29.2.1 User Configuration         | Register1(USERCFG1)               | 448 |

| 29.2.2 User Configuration         | Register2(USERCFG2)               | 448 |

| 30 Debug(DBG)                     |                                   | 450 |

| 30.1 SWD Describes the debug      | ging interface                    | 450 |

| 30.1.1 SWD Pin assignmen          | nt for debug interface            | 450 |

| 30.1.2 Internal pull-up and       | pull-down for SWD pins            | 450 |

| 30.2 Working principle of SWD p   | orotected bit                     | 450 |

| 30.3 Use SWDS in low power m      | node                              | 451 |

| 30.3.1 Using SWD in sleep         | mode(Sleep Mode)                  | 451 |

| 30.3.2 Use SWD in Deep S          | Sleep Mode                        | 451 |

| 30.4 DBG Registers                |                                   | 451 |

| 30.5 Debug Mode Control Regis     | ster(DBG_APBFZ)                   | 451 |

| 31 SysTick timer(SYST)            |                                   | 454 |

| 31.1 SysTick Introduction         |                                   | 454 |

| 31.2 Set SysTick                  |                                   | 454 |

| 31.3 SysTick Register             |                                   | 454 |

| 31.4 SysTick Register Description | on                                | 455 |

| 31.4.1 SysTickTimer Contr         | rol and Status Register(SYST_CSR) | 455 |

| 31.4.2 SysTickTimer Reloa         | ad Value Register(SYST_RVR)       | 455 |

| 31.4.3 SysTickTimer curre         | nt value register(SYST_CVR)       | 455 |

| MG32I | 003xx | llcer | Guide | \/1 | n |

|-------|-------|-------|-------|-----|---|

| 31.4.4 SysTickTimer calibration value register(SYST_CALIB) | 455             |

|------------------------------------------------------------|-----------------|

|                                                            |                 |

| 32 Version                                                 | 456             |

| <b>VL V</b> (131011                                        | <del>-</del> 00 |

#### Introduction

This reference manual provides detailed information on how to use memory and peripherals of MG32L003xx series microcontroller ( MG32L003 ), including internal structure of each function mod-ule, description of all possible functions, usage of various working modes and register configuration to help users solve application problems

MG32L003xx series microcontrollers have different memory capacities, packages and peripheral configurations. The configurations mentioned in this reference manual are only the highest of the series.

For the memory capacity, package and peripheral configuration, electrical and physical performance parameters of the MG32L003xx series, please refer to the data manual of the specific model of the series.

Download the relevant information:

http://www.megawin.com.tw/

This document is only used to help users understand and use the product, and does not assume any loss or damage caused by the use of any information in this document or any incorrect use of the product!

## 1 Document convention

# 1.1 The list of abbreviations used in the register description table

The following abbreviations are used in the description of the register:

Tab 1.1-1 Abbreviated list

| Abbreviation | Full name          | Description                                                                                                            |  |

|--------------|--------------------|------------------------------------------------------------------------------------------------------------------------|--|

| R            | read-only          | Software can only read this bit                                                                                        |  |

| W            | write-only         | Software can only write this bit                                                                                       |  |

| RW           | read/write         | Software can read and write this bit                                                                                   |  |

| RC_W0        | read/clear write0  | Software can read this bit or clear it by writing '0'. Writing '1' has no effect on this bit                           |  |

| RC_W1        | read/clear write1  | Software can read this bit or clear it by writing '1'. Writing '0' has no effect on this bit                           |  |

| RC_R         | read/clear by read | Software can read this bit. When this bit is read, it will be cleared automatically. Writing has no effect on this bit |  |

| RS_R         | read/set by read   | Software can read this bit. When this bit is read, it is automatically set. Writing has no effect on this bit.         |  |

| RS           | read/set           | Software can read or set this bit, write '0' has no effect on this bit                                                 |  |

| S            | set                | The software can only set this bit. Writing '0' has no effect on this bit                                              |  |

| Т            | toggle             | The software can only flip this bit by writing '1'. Writing '0' has no effect on this bit                              |  |

| Res.         | Reserved           | Reserved bit.                                                                                                          |  |

## 2 Memory and bus architecture

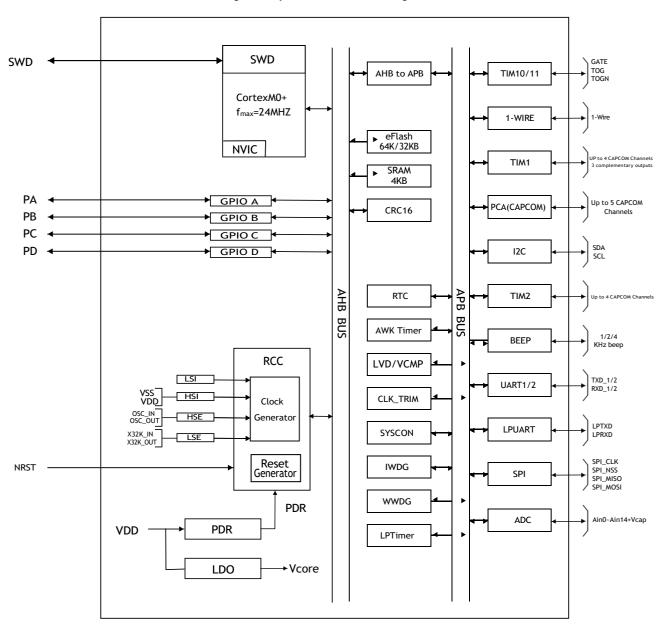

# 2.1 system structure

The system mainly consists of the following parts:

- 1 AHB Bus master

- Cortex M0+Core

- 6 AHB slave units:

- Internal SRAM

- internal flash

- AHB to APB bridge to connect all APB peripherals

- GPIOs

- Clock and Reset Control

- CRC module

These are interconnected through a multi-layer bus architecture as follows 2.1-1:

Fig 2.1-1 System architecture diagram

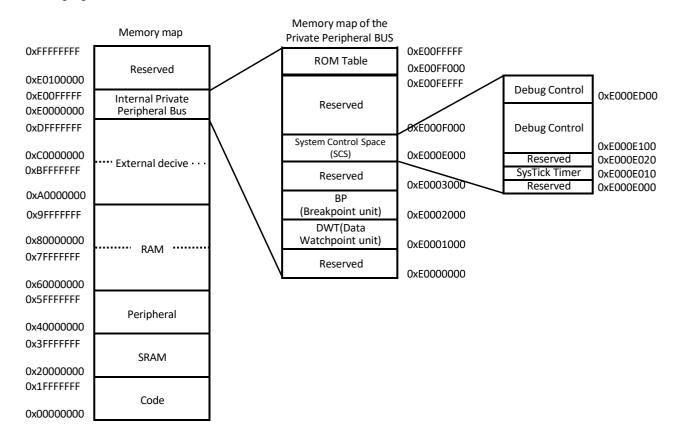

## 2.2 Storage Address

MG32L003xx embed 64/32KB Flash memory for storing user application code and data. The kernel runs on 24MHz and below,Flash do not need wait cycle.

MG32L003xx embeds 4KB of SRA Mmemory without wait cycles.

Tab 2.2-1 **Storage Address**

| Bus  | Addresses                 | Module               | Size (bytes) |

|------|---------------------------|----------------------|--------------|

|      | 0xE000_0000 - 0xE00F_FFFF | M0+ Peripheral       | 1MB          |

|      | 0x4003_0000 - 0xDFFF_FFF  | Reserved             |              |

|      | 0x4002_1000 - 0x4002_1FFF | GPIOD                | 1K           |

|      | 0x4002_1000 - 0x4002_1BFF | GPIOC                | 1K           |

|      | 0x4002_1000 - 0x4002_17FF | GPIOB                | 1K           |

| ALID | 0x4002_1000 - 0x4002_13FF | GPIOA                | 1K           |

| AHB  | 0x4002_0C00 - 0x4002_0FFF | Reserved             | 1K           |

|      | 0x4002_0800 - 0x4002_0BFF | CRC16                | 1K           |

|      | 0x4002_0400 - 0x4002_07FF | FMC                  | 1K           |

|      | 0x4002_0000 - 0x4002_03FF | RCC                  | 1K           |

|      | 0x4000_5400 - 0x4001_FFFF | Reserved             |              |

|      | 0x4000_5000 - 0x4000_53FF | LPUART               | 1K           |

|      | 0x4000_4C00 - 0x4000_4FFF | DEBUG                | 1K           |

|      | 0x4000_4800 - 0x4000_4BFF | BEEP                 | 1K           |

|      | 0x4000_4400 - 0x4000_47FF | LPTIM                | 1K           |

|      | 0x4000_4000 - 0x4000_43FF | LVD/VCMP             | 1K           |

|      | 0x4000_3C00 - 0x4000_3FFF | TIM2                 | 1K           |

|      | 0x4000_3800 - 0x4000_3BFF | OWIER                | 1K           |

|      | 0x4000_3400 - 0x4000_37FF | CLKTRIM              | 1K           |

|      | 0x4000_3000 - 0x4000_33FF | RTC                  | 1K           |

|      | 0x4000_2C00 - 0x4000_2FFF | ADC                  | 1K           |

| APB  | 0x4000_2800 - 0x4000_2BFF | AWK                  | 1K           |

|      | 0x4000_2400 - 0x4000_27FF | IWDT                 | 1K           |

|      | 0x4000_2000 - 0x4000_23FF | WWDT                 | 1K           |

|      | 0x4000_1C00 - 0x4000_1FFF | SYSCON               | 1K           |

|      | 0x4000_1800 - 0x4000_1BFF | TIM10/11             | 1K           |

|      | 0x4000_1400 - 0x4000_17FF | PCA                  | 1K           |

|      | 0x4000_1000 - 0x4000_13FF | TIM1                 | 1K           |

|      | 0x4000_0C00 - 0x4000_0FFF | I2C                  | 1K           |

|      | 0x4000_0800 - 0x4000_0BFF | SPI                  | 1K           |

|      | 0x4000_0400 - 0x4000_07FF | UART2                | 1K           |

|      | 0x4000_0000 - 0x4000_03FF | UART1                | 1K           |

|      | 0x2000_1000 - 0x3FFF_FFFF | Reserved             |              |

|      | 0x2000_0000 - 0x2000_0FFF | SRAM                 | 4K           |

|      | 0x1800_0100 - 0x1FFF_FFFF | Reserved             |              |

| ALID | 0x1800_0000 - 0x1800_00FF | System configuration | 256          |

| AHB  | 0x0800_0200 - 0x17FF_FFFF | Reserved             |              |

|      | 0x0800_0000 - 0x0800_01FF | Byte option          | 512          |

|      | 0x0001_0000 - 0x07FF_FFFF | Reserved             |              |

|      | 0x0000_0000 - 0x0000_FFFF | Main flash memory    | 64K          |

#### 3 Embedded Flash (Flash)

#### 3.1 Embedded Flash Controller

MG32L003 contains 1 64K/32K embedded Flash with 128/64 sector of main storage,5 sectors of NVR area. Each sector has a capacity of 512 bytes. The main storage area of Flash is for users to store programs and data developed by users. In the NVR area, one sector is used to store system configuration values, one sector is used to store user configuration values, and the remaining2sectors are used to store system ISP program. This module supports the erase, program and read operations of Flash memory. In addition, this module supports the protection of Flash memory erase and write, and the write protection of control registers. The main memory area is used to store user's code.

NVR sector 0 1 These 2 sectors are used to store the system ISP (programmable in the system)code, the user can download the developed application program through the ISP code, the user program cannot read or erase the ISP code.

#### 3.2 Functional description

MG32L003 supports three bit width mode FLASH reading and writing:Byte(8bits),Half-word(16bits),and Word(32bits). Note that the address of Byte operation must be aligned with Byte and the target address of Half-word operation must be aligned with Half-word. (the lowest bit of the address is 0), the address of the Word operation must be aligned with Word(the lowest two bits of the address are 0). If the address of the read and write operation is not aligned according to the above method, the system will enter the Hard Fault error interrupt.

#### 3.2.1 Erase operation