USer

Guio

P

**MG32F10**x

User Guide

Verson 1.0.2 Date 2022/7/28

## **Table of Contents**

| Table of Contents                                            | 2  |

|--------------------------------------------------------------|----|

| List of Figures                                              | 20 |

| List of Tables                                               | 23 |

| 1. Documentation conventions                                 | 25 |

| 1.1. List of abbreviations for registers                     | 25 |

| 1.2. Peripheral availability                                 | 25 |

| 2. System and memory architecture                            | 26 |

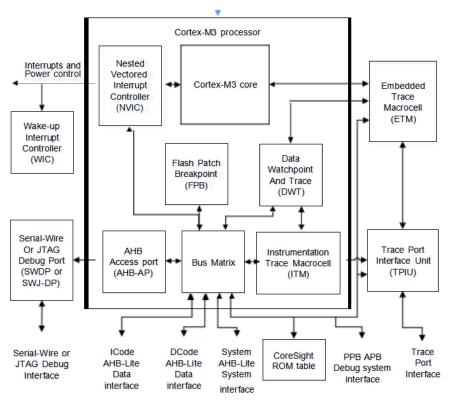

| 2.1. ARM Cortex-M3 processor                                 | 26 |

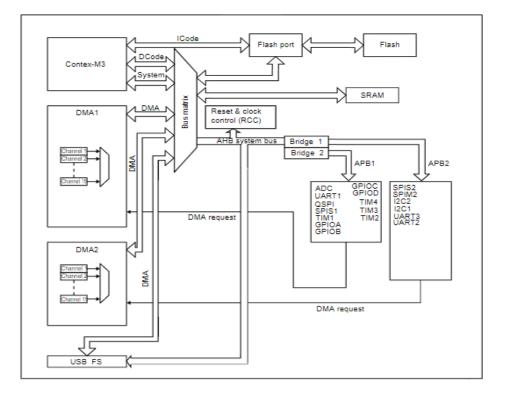

| 2.2. System architecture                                     | 27 |

| 2.3. Memory map                                              | 29 |

| 2.3.1. Bit-banding                                           | 31 |

| 2.3.2. On-chip SRAM memory                                   | 32 |

| 2.3.3. On-chip flash memory overview                         | 32 |

| 2.4. Program and Erase                                       | 33 |

| 2.5. Boot configuration                                      | 33 |

| 2.6. CACHE register                                          | 34 |

| 2.6.1. Cache Control register (CACHE_CR)                     | 34 |

| 3. System configuration (SYS)                                | 36 |

| 3.1. Overview                                                |    |

| 3.2. Main features of SYS                                    | 36 |

| 3.2.1. Security level configuration                          | 36 |

| 3.2.2. Information block write protection                    | 37 |

| 3.2.3. The write protection of system memory space           | 37 |

| 3.2.4. User program space write protection control           | 37 |

| 3.2.5. Secondary Development                                 | 39 |

| 3.3. SYS Register Description                                |    |

| 3.3.1. ID Register (SYS_ID)                                  | 40 |

| 3.3.2. Memory control Register (SYS_MEMSZ)                   | 40 |

| 3.3.3. Security control Register (SYS_BTCR)                  | 41 |

| 3.3.4. FLASH write protection register (SYS_MEMWEN)          |    |

| 3.3.5. Secondary development control Register (SYS_SENDEV)   | 41 |

| 3.3.6. Reboot control Register (SYS_RSTCR)                   | 42 |

| 3.3.7. Information block 4 protection register (SYS_IF4LCK)  | 42 |

| 3.3.8. Information block 5 protection register (SYS_IF5LCK)  | 43 |

| 3.3.9. Information block 6 protection register (SYS_IF6LCK)  |    |

| 3.3.10. Information block 7 protection register (SYS_IF7LCK) | 43 |

| 3.3.11. Boot control Register (SYS_BTSR)                     | 44 |

| 4. Cyclic Redundancy Check (CRC)                             | 45 |

| 4.1. CRC introduction                                        | 45 |

| 4.2. CRC main features                                       |    |

| 4.3. CRC register description                                | 46 |

| 4.3.1. CRC mode register (CRC_MODE)                           | 46 |

|---------------------------------------------------------------|----|

| 4.3.2. CRC seed register (CRC_SEED)                           | 46 |

| 4.3.3. CRC checksum register (CRC_SUM)                        | 47 |

| 4.3.4. CRC data register (CRC_WDATA)                          | 47 |

| 5. Random Number Generator (RNG)                              | 48 |

| 5.1. Introduction                                             | 48 |

| 5.2. Random number generator SFR                              | 48 |

| 5.2.1. Random number generator (RNG_RAND)                     | 48 |

| 5.2.2. RNG STOP register (RNG_STOP)                           | 48 |

| 5.2.3. RNG Record register (RNG_REC)                          | 48 |

| 6. Power control (PWR)                                        | 50 |

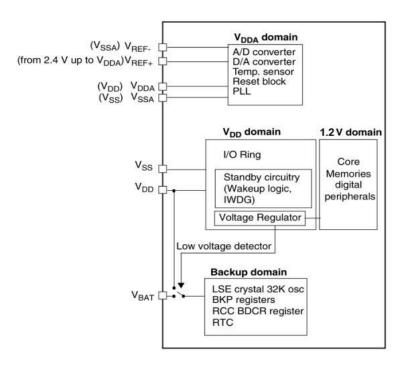

| 6.1. Power supplies                                           | 50 |

| 6.1.1. Independent A/D converter supply and reference voltage | 50 |

| 6.1.2. Battery backup domain                                  | 51 |

| 6.1.3. Voltage regulator                                      | 52 |

| 6.2. Power supply supervisor                                  | 52 |

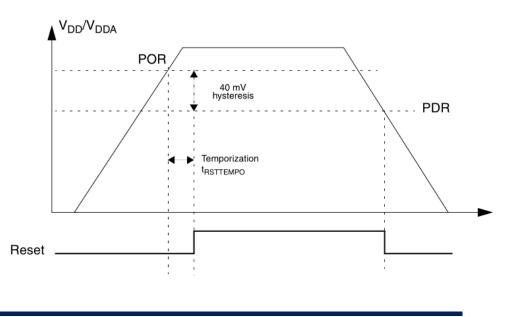

| 6.2.1. Power on reset (POR)/power down reset (PDR)            | 52 |

| 6.2.2. Programmable voltage detector                          | 53 |

| 6.3. Low-power modes                                          | 53 |

| 6.3.1. Slowing down system clocks                             | 54 |

| 6.3.2. Peripheral clock gating                                | 54 |

| 6.3.3. Sleep mode                                             | 54 |

| 6.3.4. Stop mode                                              | 56 |

| 6.3.5. Standby mode                                           |    |

| 6.3.6. Module status in low power mode                        | 60 |

| 6.3.7. Auto-wakeup (AWU) from low-power mode                  | 60 |

| 6.4. Power control registers                                  |    |

| 6.4.1. Power control register 0 (PWR_CR0)                     | 61 |

| 6.4.2. Control register 1 (PWR_CR1)                           | 63 |

| 6.4.3. Control register 2 (PWR_CR2)                           | 64 |

| 6.4.4. Status register 0 (PWR_SR0)                            |    |

| 6.4.5. Status register 1 (PWR_SR1)                            |    |

| 6.4.6. General purpose register 0 (PWR_GPREG0)                | 65 |

| 6.4.7. General purpose register 1 (PWR_GPREG1)                |    |

| 6.4.8. Configuration register (PWR_CFGR)                      |    |

| 6.4.9. Analog enable register 1 (PWR_ANAKEY 1)                |    |

| 6.4.10. Analog enable register 2 (PWR_ANAKEY 2)               |    |

| 7. Backup registers (BKP)                                     |    |

| 7.1. Overview                                                 |    |

| 7.2. Characteristics                                          |    |

| 7.3. Function overview                                        |    |

| 7.3.1. RTC clock calibration                                  |    |

| 7.3.2. RTC clock calibration                                  | 69 |

| 7.4. Register description                                     | 69 |

|         | 7.4.1. RTC signal output control register (BKP_RTCCR)                | 69 |

|---------|----------------------------------------------------------------------|----|

|         | 7.4.2. Tamper pin control register (BKP_CR)                          | 70 |

|         | 7.4.3. Tamper control and status register (BKP_CSR)                  | 70 |

|         | 7.4.4. Backup data register x (BKP_DATAx) (x= 021)                   | 71 |

|         | 7.4.5. Backup domain control register (BKP_BDCR)                     | 71 |

| 8. Rese | et and Clock Control (RCC)                                           | 73 |

| 8.1.    | Reset                                                                | 73 |

|         | 8.1.1. System reset                                                  | 73 |

|         | 8.1.2. Power source reset                                            | 73 |

|         | 8.1.3. Battery domain reset                                          | 74 |

| 8.2.    | Clock                                                                | 74 |

|         | 8.2.1. System clock source                                           | 74 |

|         | 8.2.2. Sub-clock source                                              | 74 |

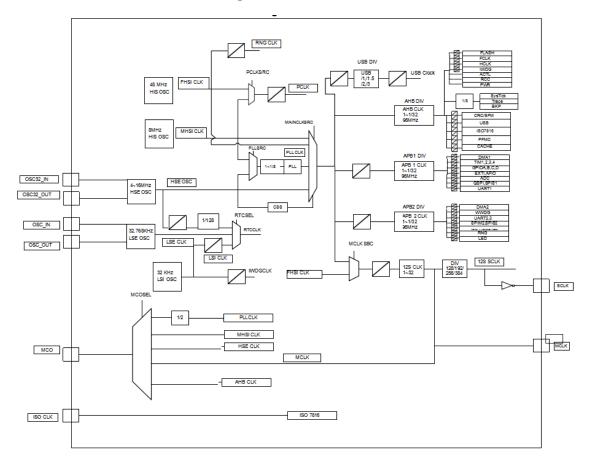

|         | 8.2.3. Clock tree                                                    | 74 |

|         | 8.2.4. HSE clock                                                     | 75 |

|         | 8.2.5. HSI clock                                                     | 76 |

|         | 8.2.6. PLL clock                                                     | 76 |

|         | 8.2.7. LSE clock                                                     | 76 |

|         | 8.2.8. LSI clock                                                     | 77 |

|         | 8.2.9. System clock MAINCLK selection                                | 77 |

|         | 8.2.10. Clock Security System CSS                                    | 77 |

|         | 8.2.11. RTC clock                                                    | 77 |

|         | 8.2.12. IWDG clock                                                   | 78 |

|         | 8.2.13. Clock-out capability                                         | 78 |

|         | 8.2.14. Bus clock switch and divider                                 | 78 |

| 8.3.    | RCC registers                                                        | 78 |

|         | 8.3.1. PLL pre-divider control register (RCC_PLLPRE)                 | 78 |

|         | 8.3.2. PLL clock source selection register (RCC_PLLSRC)              | 79 |

|         | 8.3.3. System clock source selection register (RCC_MAINCLKSRC)       | 79 |

|         | 8.3.4. System clock source update enable register (RCC_MAINCLKUEN)   | 80 |

|         | 8.3.5. USB clock pre-divider control register (RCC_USBPRE)           | 80 |

|         | 8.3.6. AHB clock pre-divider register (RCC_AHBPRE)                   | 80 |

|         | 8.3.7. APB1 clock pre-divider control register (RCC_APB1PRE)         | 81 |

|         | 8.3.8. APB2 clock pre-divider control register (RCC_APB2PRE)         | 81 |

|         | 8.3.9. I2S MCLK clock pre-divider control register (RCC_MCLKPRE)     | 82 |

|         | 8.3.10. I2S SCLK clock pre-divider control register (RCC_I2SPRE)     | 82 |

|         | 8.3.11. I2S MCLK clock source selection register (RCC_MCLKSRC)       |    |

|         | 8.3.12. USB FIFO clock source selection register (RCC_USBFIFOCLKSRC) |    |

|         | 8.3.13. Clock output selection register (RCC_MCOSEL)                 |    |

|         | 8.3.14. AHB peripherals clock enable register0 (RCC_AHBENR0)         |    |

|         | 8.3.15. AHB peripherals clock enable register1 (RCC_AHBENR1)         |    |

|         | 8.3.16. AHB peripherals clock enable register2 (RCC_AHBENR2)         |    |

|         | 8.3.17. APB1 peripherals clock enable register (RCC_APB1ENR)         |    |

|         | 8.3.18. APB2 peripherals clock enable register (RCC_APB2ENR)         | 86 |

|         | 8.3.19. RNG clock enable register (RCC_RNGCLKENR)                 | 86 |

|---------|-------------------------------------------------------------------|----|

|         | 8.3.20. IWDG clock enable register (RCC_IWDGCLKENR)               | 87 |

|         | 8.3.21. USB48MHz clock enable register (RCC_USBCLKENR)            | 87 |

|         | 8.3.22. I2S SCLK clock enable register (RCC_I2SCLKENR)            | 87 |

|         | 8.3.23. SPIS1 clock enable register (RCC_SPIS1CLKENR)             | 88 |

|         | 8.3.24. SPIS2 clock enable register (RCC_SPIS2CLKENR)             | 88 |

|         | 8.3.25. USB FIFO clock enable register (RCC_USBFIFOCLKENR)        | 88 |

|         | 8.3.26. AHB peripheral reset register1 (RCC_AHBRSTR1)             | 89 |

|         | 8.3.27. APB1 peripheral reset register(RCC_APB1RSTR)              | 89 |

|         | 8.3.28. APB2 peripheral reset register (RCC_APB2RSTR)             | 90 |

|         | 8.3.29. I2S SCLK reset register (RCC_I2SCLKRSTR)                  | 90 |

|         | 8.3.30. Reset flag clear register (RCC_CLRRSTSTAT)                | 91 |

|         | 8.3.31. Battery domain reset register (RCC_BDRSTR)                | 91 |

|         | 8.3.32. LSI battery domain clock enable register (RCC_LSI2RTCENR) | 91 |

|         | 8.3.33. HSE clock 128-divider enable register (RCC_HSE2RTCENR)    | 92 |

|         | 8.3.34. Reset flag register (RCC_RSTSTAT)                         | 92 |

| 9. Gene | ral-purpose and alternate-function I/Os (GPIOs and AFIOs)         | 93 |

| 9.1.    | Introduction                                                      | 93 |

| 9.2.    | GPIO main features                                                | 93 |

| 9.3.    | GPIO functional description                                       | 94 |

|         | 9.3.1. General-purpose I/O (GPIO)                                 | 95 |

|         | 9.3.2. I/O pin alternate function multiplexer and mapping         |    |

|         | 9.3.3. I/O port control registers                                 |    |

|         | 9.3.4. I/O port data registers                                    | 97 |

|         | 9.3.5. I/O data bit handling                                      | 97 |

|         | 9.3.6. GPIO locking mechanism                                     | 98 |

|         | 9.3.7. I/O alternate function input/output                        | 98 |

|         | 9.3.8. External interrupt/wakeup lines1                           | 01 |

|         | 9.3.9. Input configuration1                                       | 01 |

|         | 9.3.10. Output configuration1                                     |    |

|         | 9.3.11. Alternate function configuration1                         |    |

|         | 9.3.12. Analog configuration1                                     |    |

|         | 9.3.13. Using the HSE or LSE oscillator pins as GPIOs1            |    |

|         | 9.3.14. Using the GPIO pins in the backup supply domain1          |    |

| 9.4.    | GPIO registers1                                                   | 03 |

|         | 9.4.1. GPIO port mode register (GPIOx_MODER)1                     | 03 |

|         | 9.4.2. GPIO port output type register (GPIOx_OTYPER)1             | 03 |

|         | 9.4.3. GPIO port output speed register (GPIOx_OSPEEDR)1           | 04 |

|         | 9.4.4. GPIO port pull-up/pull-down register (GPIOx_PUPDR)1        | 04 |

| 9.4.5. GPIO port input data register (GPIOx_IDR)104                  |

|----------------------------------------------------------------------|

| 9.4.6. GPIO port output data register (GPIOx_ODR)105                 |

| 9.4.7. GPIO port bit set/reset register (GPIOx_BSRR)105              |

| 9.4.8. GPIO port configuration lock register (GPIOx_LCKR)105         |

| 9.4.9. GPIO alternate function low register (GPIOx_AFRL)106          |

| 9.4.10. GPIO alternate function high register (GPIOx_AFRH)107        |

| 9.4.11. GPIO Port Schmitt Register (GPIOx_SMIT)107                   |

| 9.4.12. GPIO Port driver register (GPIOx_CURRENT)108                 |

| 9.4.13. GPIO Port configuration auxiliary register (GPIOx_CFGMSK)108 |

| 9.5. AFIO registers108                                               |

| 9.5.1. External interrupt configuration register 1 (AFIO_EXTICR1)108 |

| 9.5.2. External interrupt configuration register 2 (AFIO_EXTICR2)109 |

| 9.5.3. External interrupt configuration register 3 (AFIO_EXTICR3)109 |

| 9.5.4. External interrupt configuration register 4 (AFIO_EXTICR4)110 |

| 10. Nested vectored interrupt controller (NVIC)111                   |

| 10.1. NVIC Features 111                                              |

| 10.2. Interrupt and exception vectors                                |

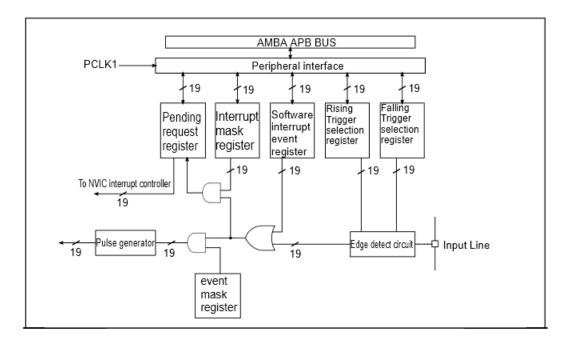

| 11. Interrupt/event controller (EXTI)                                |

| 11.1. Overview                                                       |

| 11.2. Characteristics                                                |

| 11.3. External interrupt and event (EXTI) block diagram              |

| 11.4. External Interrupt and Event function overview                 |

| 11.5.1. Interrupt enable register (EXTI_INTEN)                       |

| 11.5.2. Event enable register (EXTI_EMR)                             |

| 11.5.3. Rising edge trigger enable register (EXTI_RTSR)              |

| 11.5.4. Falling edge trigger enable register (EXTI_FTSR)             |

| 11.5.5. Software interrupt event register (EXTI_SWIER)               |

| 11.5.6. Pending register (EXTI_PR)                                   |

| 12. Analog control (ANCTL)                                           |

| 12.1. Analog control introduction                                    |

|     | 12.2. Analog control major features           | 119 |

|-----|-----------------------------------------------|-----|

|     | 12.3. Analog control function description     | 119 |

|     | 12.3.1. MHSI control                          | 119 |

|     | 12.3.2. FHSI control                          | 119 |

|     | 12.3.3. LSI control                           | 119 |

|     | 12.3.4. HSE control                           | 120 |

|     | 12.3.5. Phase locked loop (PLL)               | 120 |

|     | 12.3.6. PVD control                           |     |

|     | 12.3.7. SARADC control                        | 121 |

|     | 12.3.8. Analog Comparator (CMP) control       | 121 |

|     | 12.3.9. CSS control                           | 123 |

|     | 12.4. Register definition                     | 123 |

|     | 12.4.1. BG control SFR2 (ANCTL_BGCR2)         | 123 |

|     | 12.4.2. MHSI enable SFR (ANCTL_MHSIENR)       | 123 |

|     | 12.4.3. MHSI Status SFR (ANCTL_MHSISR)        | 123 |

|     | 12.4.4. FHSI enable SFR (ANCTL_FHSIENR)       | 124 |

|     | 12.4.5. FHSI Status SFR (ANCTL_FHSISR)        | 124 |

|     | 12.4.6. LSI enable SFR (ANCTL_LSIENR)         | 124 |

|     | 12.4.7. LSI Status SFR (ANCTL_LSISR)          | 124 |

|     | 12.4.8. HSE control SFR 0 (ANCTL_HSECR0)      | 125 |

|     | 12.4.9. HSE control SFR 1 (ANCTL_HSECR1)      | 125 |

|     | 12.4.10. HSE Status SFR (ANCTL_HSESR)         | 125 |

|     | 12.4.11. PLL control SFR (ANCTL_PLLCR)        | 125 |

|     | 12.4.12. PLL enable SFR (ANCTL_PLLENR)        | 126 |

|     | 12.4.13. PLL Status SFR (ANCTL_PLLSR)         | 126 |

|     | 12.4.14. PVD control SFR (ANCTL_PVDCR)        | 126 |

|     | 12.4.15. PVD enable SFR (ANCTL_PVDENR)        | 126 |

|     | 12.4.16. SARADC enable SFR (ANCTL_SARENR)     | 127 |

|     | 12.4.17. POR control SFR (ANCTL_PORCR)        | 127 |

|     | 12.4.18. CMPA control SFR (ANCTL_CMPACR)      | 127 |

|     | 12.4.19. CMPB control SFR (ANCTL_CMPBCR)      |     |

|     | 12.4.20. INT Status SFR (ANCTL_ISR)           |     |

|     | 12.4.21. INT enable SFR (ANCTL_IER)           | 129 |

|     | 12.4.22. INT clear SFR (ANCTL_ICR)            |     |

|     | 12.4.23. CMPA Status SFR (ANCTL_CMPASR)       |     |

|     | 12.4.24. CMPB Status SFR (ANCTL_CMPBSR)       | 130 |

|     | 12.4.25. CSS enable SFR (ANCTL_CSSENR)        | 130 |

|     | 12.4.26. CSS configuration SFR (ANCTL_CSSCR)  |     |

| 13. | . Special Function Macro (SFM)                | 131 |

|     | 13.1. SFM Introduction                        | 131 |

|     | 13.1.1. SFM main features                     | 131 |

|     | 13.2. Function description                    | 131 |

|     | 13.2.1. Count the number of "1"               | 131 |

|     | 13.2.2. Expand all the bits in a WORD (32bit) | 131 |

|     |                                               |     |

| 13.2.3. USB port status detection and interrupt control                   | 131 |

|---------------------------------------------------------------------------|-----|

| 13.3. Register definition                                                 | 131 |

| 13.3.1. Control register(SFM_CTRL)                                        | 131 |

| 13.3.2. SFM Data register (SFM_DATA)                                      | 132 |

| 13.3.3. SFM Result register (SFM_DOUTx, x=0-7)                            | 132 |

| 13.3.4. USB port status detection control/status register (SFM_USBPSDCSR) |     |

| 13.3.5. USB Port status register (SFM_USBPSTAT)                           | 133 |

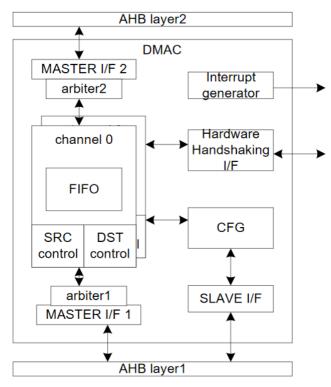

| 14. Direct Memory access Controller (DMAC)                                | 134 |

| 14.1. Overview                                                            | 134 |

| 14.2. Characteristics                                                     | 134 |

| 14.3. Pre-Configuration                                                   | 135 |

| 14.4. Block Diagram                                                       | 135 |

| 14.5. Function Overview                                                   | 136 |

| 14.5.1. DMA operation                                                     | 136 |

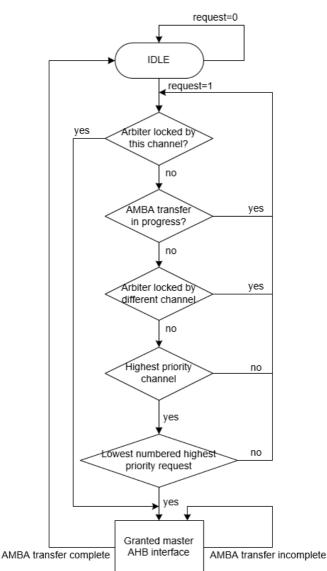

| 14.5.2. Arbitration for AHB master interface                              | 136 |

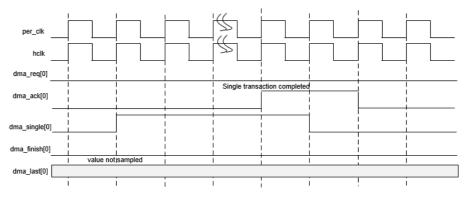

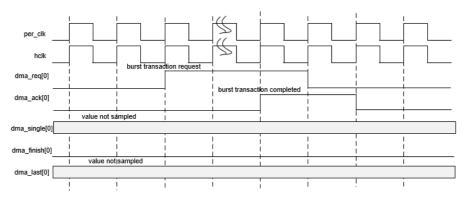

| 14.5.3. DMA Handshaking                                                   | 138 |

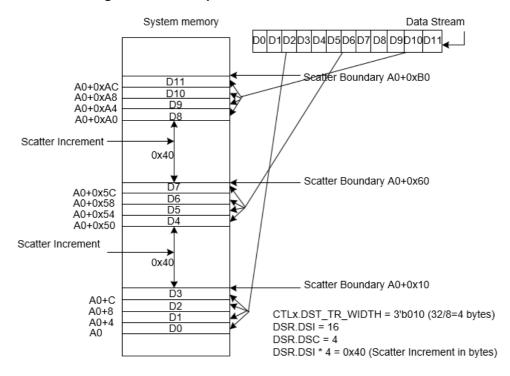

| 14.5.4. Scatter                                                           | 140 |

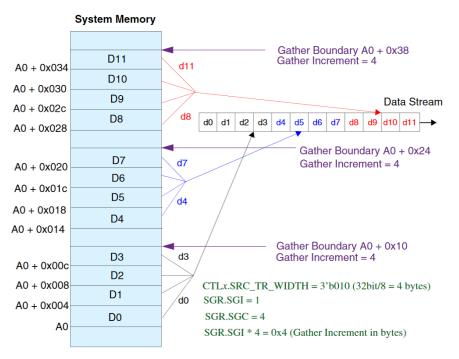

| 14.5.5. Gather                                                            | 140 |

| 14.5.6. AHB Transfer Error Handling                                       | 141 |

| 14.5.7. Disabling a Channel Prior to Transfer Completion                  | 142 |

| 14.5.8. Programming Examples                                              |     |

| 14.5.9. Interrupt                                                         | 144 |

| 14.5.10. DMA Request Mapping                                              | 144 |

| 14.6. DMA Registers                                                       | 146 |

| 14.6.1. Source Address for Channel x: SARx (x=0,1,2)                      | 146 |

| 14.6.2. Destination Address for Channel x: DARx (x=0,1,2)                 |     |

| 14.6.3. Channel Control register Low: CTLLx (x=0,1,2)                     |     |

| 14.6.4. Channel Control register High: CTLHx (x=0,1,2)                    |     |

| 14.6.5. Channel Configuration register Low: CFGLx (x=0,1,2)               |     |

| 14.6.6. Channel Configuration register High: CFGHx (x=0,1,2)              | 150 |

| 14.6.7. Source Gather Register: SGRx (x=0,1,2)                            |     |

| 14.6.8. Destination Scatter Register: DSRx (x=0,1,2)                      | 152 |

| 14.6.9. Interrupt Raw Status Register:                                    | 152 |

| 14.6.10. Interrupt Status Register                                        | 152 |

| 14.6.11. Interrupt Mask Register                                          | 153 |

| 14.6.12. Interrupt Clear Register                                         | 154 |

| 14.6.13. Status for each Interrupt type: StatusInt                        |     |

| 14.6.14. Source Software Transaction Request register: ReqSrcReg          |     |

| 14.6.15. Destination Software Transaction Request register: ReqDstReg     | 156 |

| 14.6.16. Source Single Transaction Request register: SglRqSrcReg          |     |

| 14.6.17. Destination Single Transaction Request register: SglRqDstReg     |     |

| 14.6.18. Source Last Transaction Request register: LstSrcReg              |     |

| 14.6.19. Destination Last Transaction Request register: LstDstReg         |     |

| 14.6.20. DMA Configuration Register: DmaCfgReg                            |     |

|     | 14.6.21. Channel Enable register: ChEnReg                                | 160 |

|-----|--------------------------------------------------------------------------|-----|

|     | 14.6.22. DMA ID register0: DmaCompsID0                                   | 160 |

|     | 14.6.23. DMA ID register1: DmaCompsID1                                   | 161 |

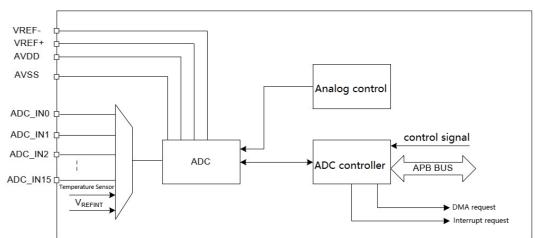

| 15. | Analog to digital conversion (ADC)                                       | 162 |

|     | 15.1. ADC introduction                                                   | 162 |

|     | 15.2. ADC main features                                                  | 162 |

|     | 15.3. ADC functional description                                         | 162 |

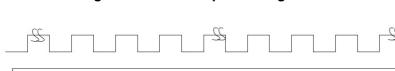

|     | 15.3.1. ADC on-off control                                               | 163 |

|     | 15.3.2. ADC clock                                                        | 163 |

|     | 15.3.3. ADC resolution                                                   | 164 |

|     | 15.3.4. Channel selection                                                | 164 |

|     | 15.3.5. Single conversion mode                                           | 164 |

|     | 15.3.6. Continuous conversion mode                                       | 165 |

|     | 15.3.7. Timing diagram                                                   | 165 |

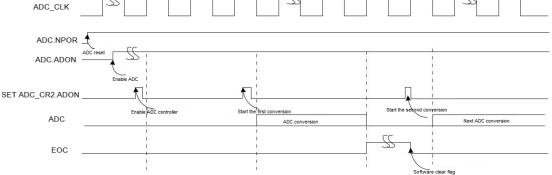

|     | 15.3.8. Analog watchdog                                                  | 165 |

|     | 15.3.9. Scan mode                                                        | 166 |

|     | 15.3.10. Injected channel management                                     | 167 |

|     | 15.3.11. Discontinuous mode                                              | 167 |

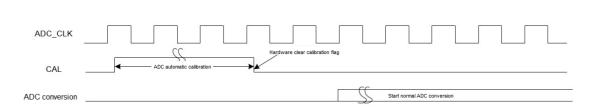

|     | 15.4. Calibration                                                        | 168 |

|     | 15.5. Data alignment                                                     | 169 |

|     | 15.6. Channel-by-channel programmable sample time                        | 170 |

|     | 15.7. Conversion on external trigger                                     | 170 |

|     | 15.8. DMA request                                                        | 171 |

|     | 15.9. Temperature sensor                                                 | 171 |

|     | 15.10. ADC interrupts                                                    | 172 |

|     | 15.11. ADC registers                                                     |     |

|     | 15.11.1. ADC status register (ADC_SR)                                    |     |

|     | 15.11.2. ADC control register 1(ADC_CR1)                                 |     |

|     | 15.11.3. ADC control register 2(ADC_CR2)                                 | 176 |

|     | 15.11.4. ADC sample time register 1(ADC_SMPR1)                           |     |

|     | 15.11.5. ADC sample time register2(ADC_SMPR2)                            | 179 |

|     | 15.11.6. ADC injected channel data offset register x (ADC_JOFRx) (x =14) | 179 |

|     | 15.11.7. ADC watchdog high threshold register (ADC_HTR)                  | 180 |

|     | 15.11.8. ADC watchdog low threshold register (ADC_LTR)                   | 180 |

|     | 15.11.9. ADC regular sequence register 1 (ADC_SQR1)                      | 180 |

|     | 15.11.10. ADC regular sequence register 2 (ADC_SQR2)                     | 181 |

|     | 15.11.11. ADC regular sequence register 3 (ADC_SQR3)                     | 181 |

|     | 15.11.12. ADC injected sequence register (0ADC_JSQR)                     | 182 |

|     | 15.11.13. ADC injected data register x (ADC_JDRx) (x=14)                 | 182 |

|     | 15.11.14. ADC regular data register (ADC_DR)                             | 182 |

|     | 15.11.15. ADC control register 3(ADC_CR3)                                | 183 |

|     | 15.11.16. ADC injected convertion DMA register (ADC_JDMAR)               | 183 |

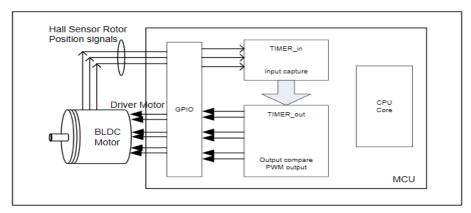

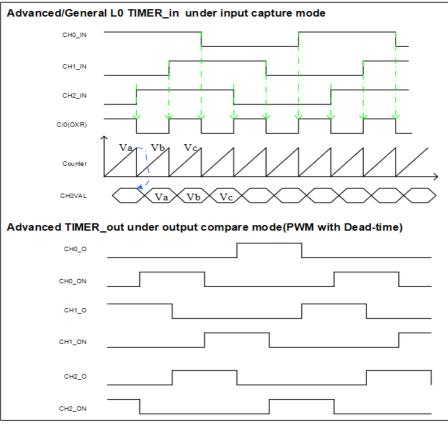

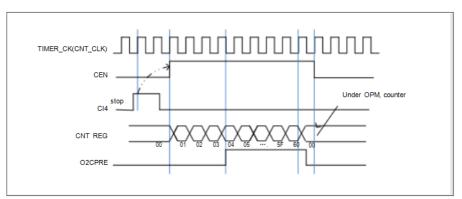

| 16. | Advanced timer (TIM1)                                                    | 184 |

| 16.1. Overview                                                 |     |

|----------------------------------------------------------------|-----|

| 16.2. Characteristics                                          |     |

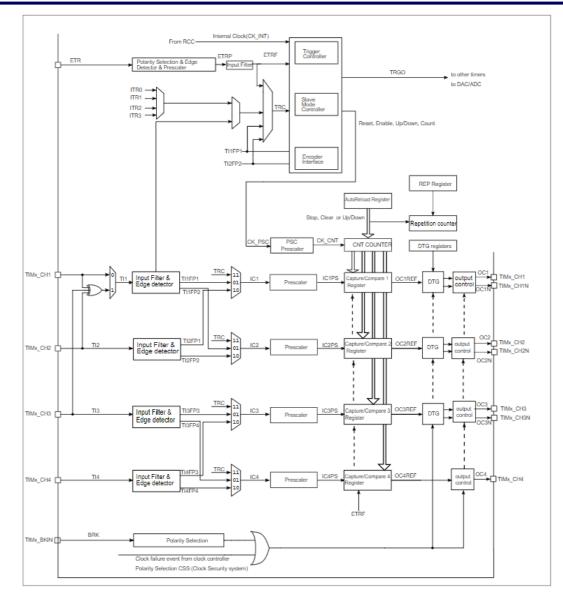

| 16.3. Block diagram                                            |     |

| 16.4. Function overview                                        |     |

| 16.4.1. Clock selection                                        |     |

| 16.4.2. Prescaler                                              |     |

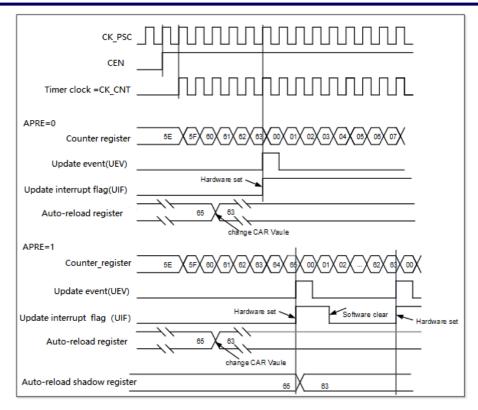

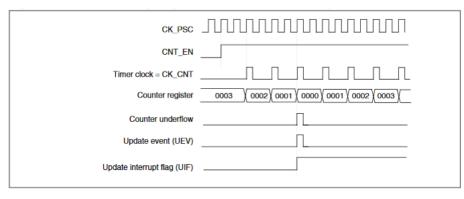

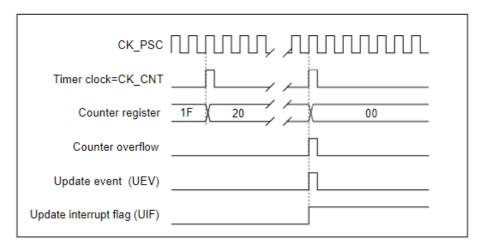

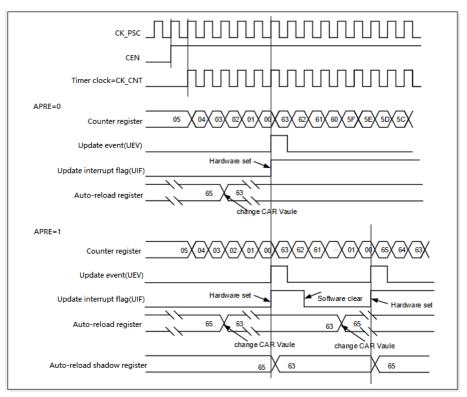

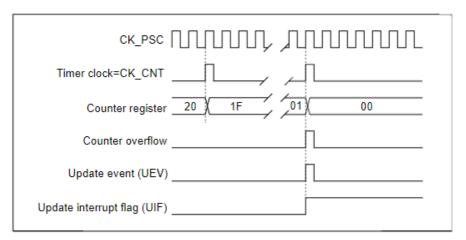

| 16.4.3. Up counting mode                                       |     |

| 16.4.4. Down counting mode                                     |     |

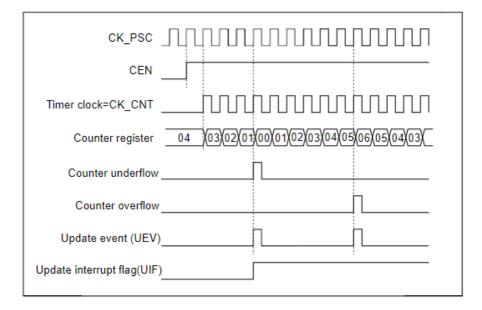

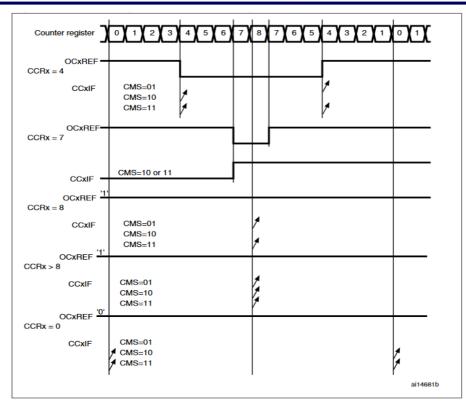

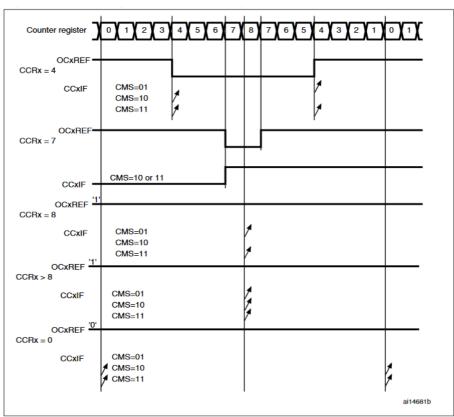

| 16.4.5. Center-aligned counting mode                           |     |

| 16.4.6. Counter repetition                                     |     |

| 16.4.7. Capture/compare channels                               |     |

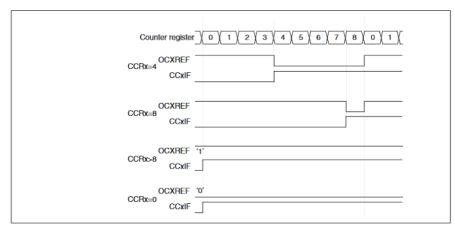

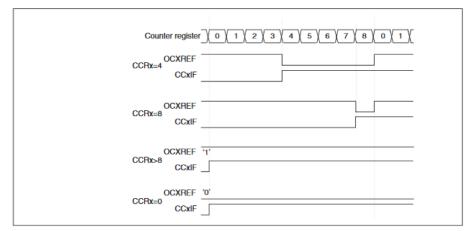

| 16.4.8. PWM mode                                               |     |

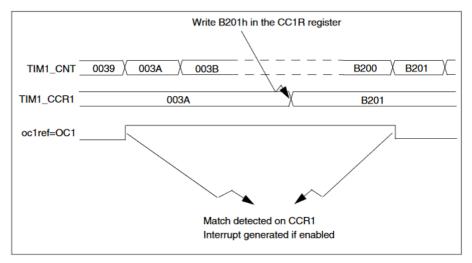

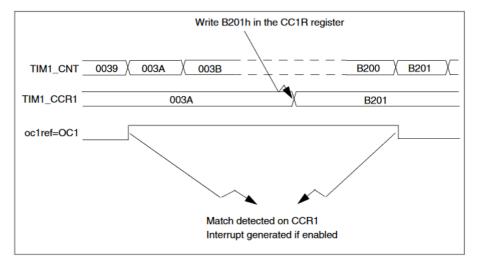

| 16.4.9. Channel output reference signal                        |     |

| 16.4.10. Outputs complementary                                 |     |

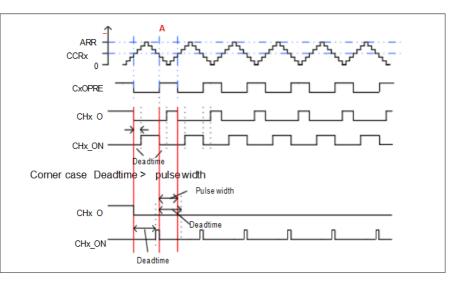

| 16.4.11. Dead time insertion                                   |     |

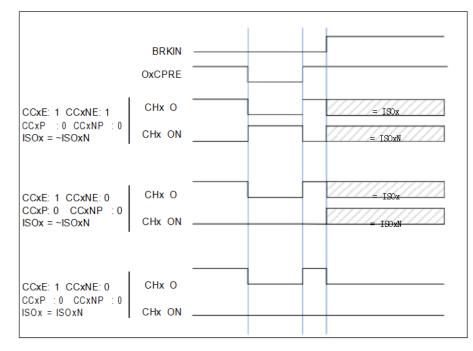

| 16.4.12. Break function                                        |     |

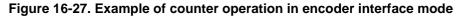

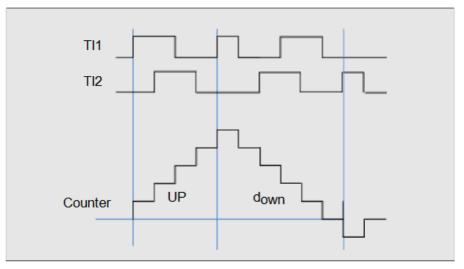

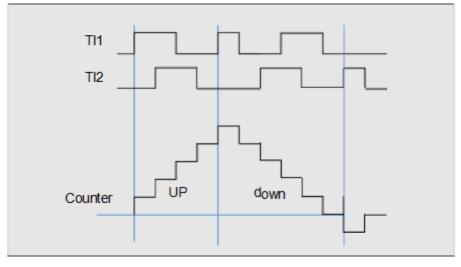

| 16.4.13. Quadrature decoder                                    |     |

| 16.4.14. Hall sensor function                                  |     |

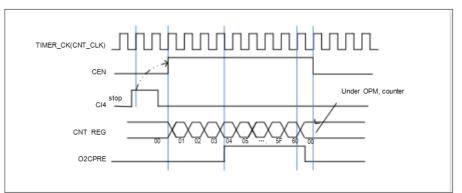

| 16.4.15. Single pulse mode                                     |     |

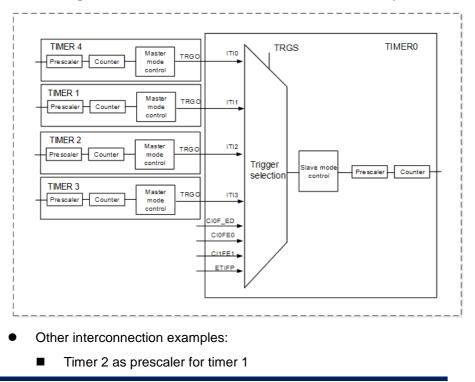

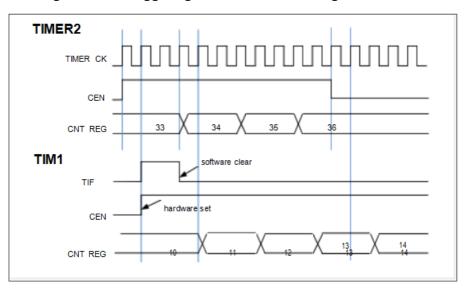

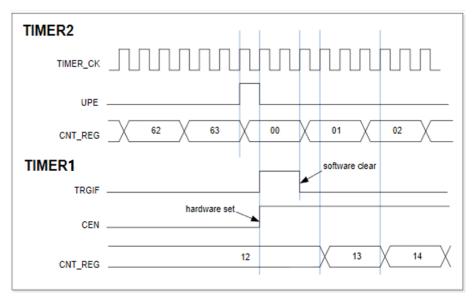

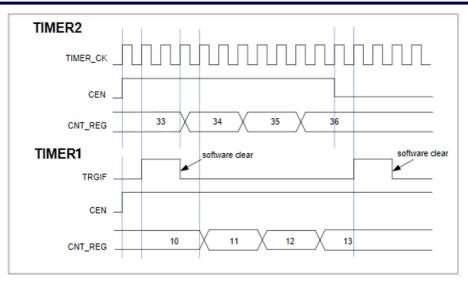

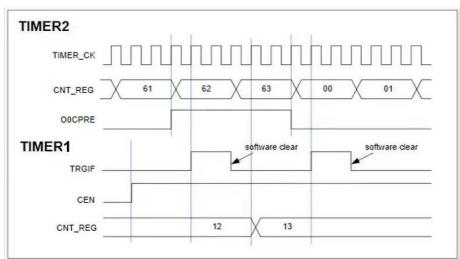

| 16.4.16. Timers interconnection                                |     |

| 16.4.17. Timer DMA mode                                        | 213 |

| 16.4.18. Timer debug mode                                      |     |

| 16.5. Register definition                                      | 213 |

| 16.5.1. Control register 1 (TIMx_CR1)                          | 213 |

| 16.5.2. Control register 2 (TIMx_CR2)                          | 214 |

| 16.5.3. Slave mode configuration register (TIMx_SMCR)          | 216 |

| 16.5.4. DMA and interrupt enable register (TIMx_DIER)          | 218 |

| 16.5.5. Interrupt flag register (TIMx_SR)                      |     |

| 16.5.6. Software event generation register (TIMx_EGR)          |     |

| 16.5.7. Channel control register 0 (TIMx_CCMR1)                |     |

| 16.5.8. Channel control register 1 (TIMx_CCMR2)                |     |

| 16.5.9. Channel control register 2 (TIMx_CCER)                 |     |

| 16.5.10. Counter register (TIMx_CNT)                           |     |

| 16.5.11. Prescaler register (TIMx_PSC)                         |     |

| 16.5.12. Counter auto reload register (TIMx_ARR)               |     |

| 16.5.13. Counter repetition register (TIMx_RCR)                |     |

| 16.5.14. Channel 1 capture/compare value register (TIMx_CCR1)  |     |

| 16.5.15. Channel 2 capture/compare value register (TIMx_CCR2)  |     |

| 16.5.16. Channel 3 capture/compare value register (TIMx_CCR3)  |     |

| 16.5.17. Channel 4 capture/compare value register (TIMx_CCR4)  |     |

| 16.5.18. Complementary channel protection register (TIMx_BDTR) |     |

| 17. General-Purpose Timers (TIM2-TIM4)                         |     |

| 17.1. Overview                                                 |     |

| 17.2. Characteristics                                          |     |

|     | 17.3. Block diagram                                           | 233 |

|-----|---------------------------------------------------------------|-----|

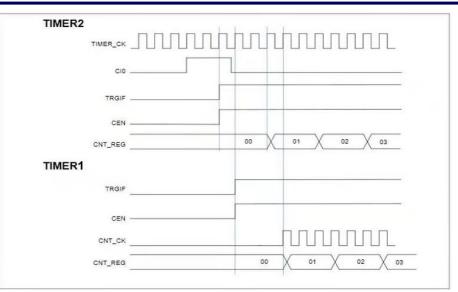

|     | 17.4. Function overview                                       | 234 |

|     | 17.4.1. Clock selection                                       | 234 |

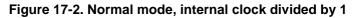

|     | 17.4.2. Prescaler                                             | 235 |

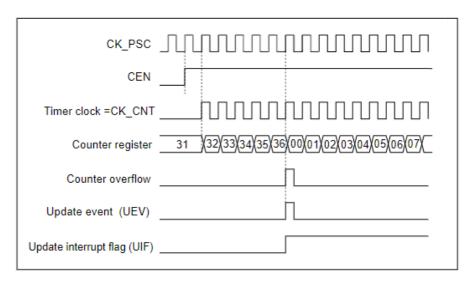

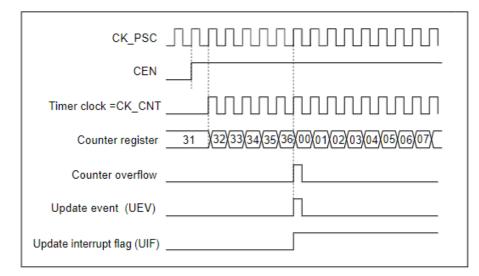

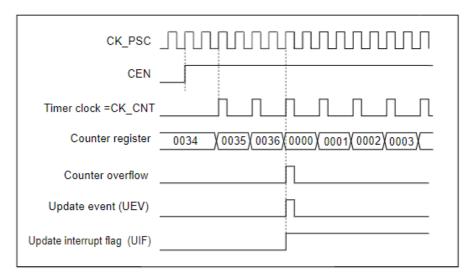

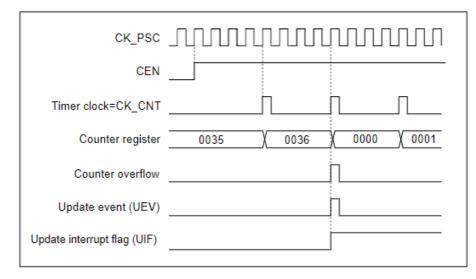

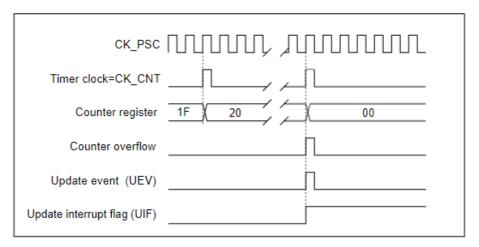

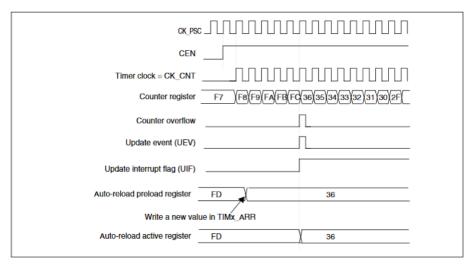

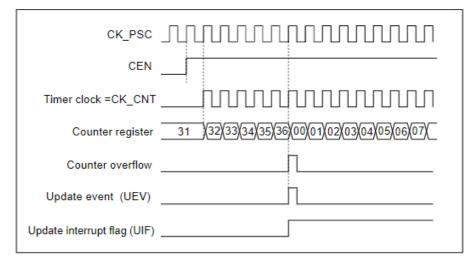

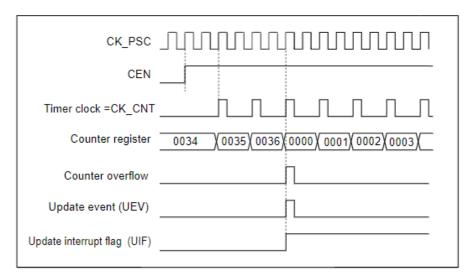

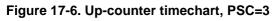

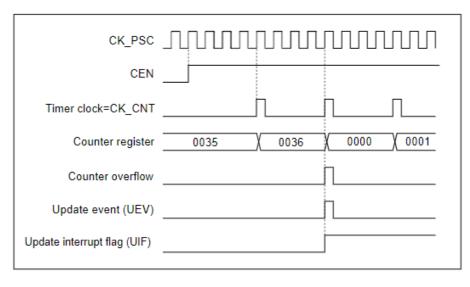

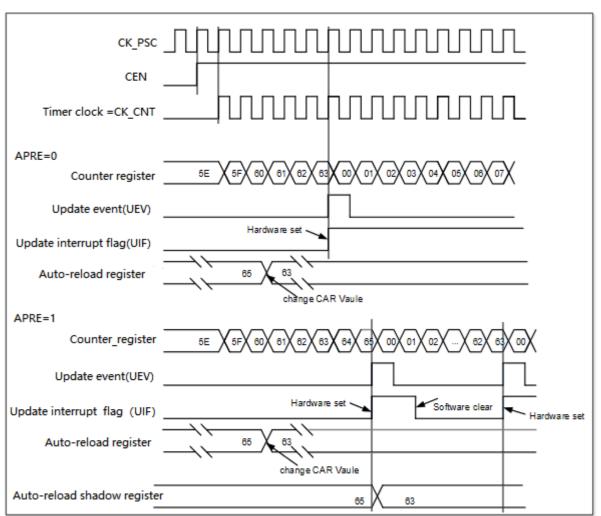

|     | 17.4.3. Up counting mode                                      | 235 |

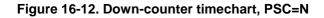

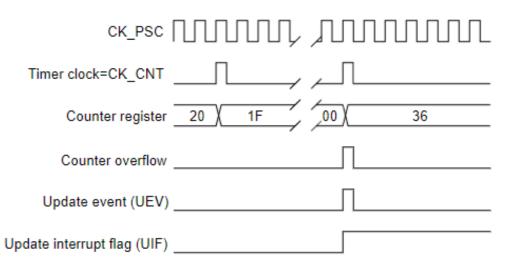

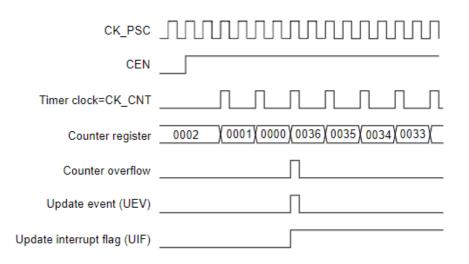

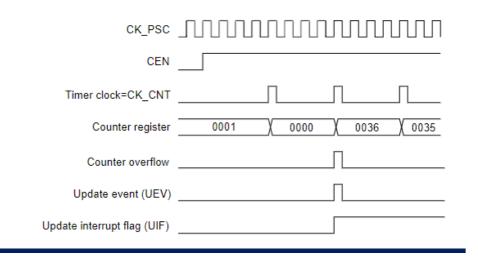

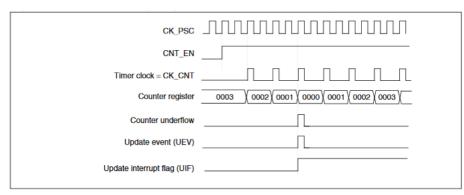

|     | 17.4.4. Down counting mode                                    | 238 |

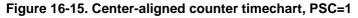

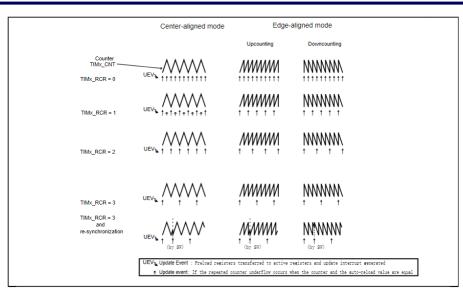

|     | 17.4.5. Center-aligned counting mode                          | 240 |

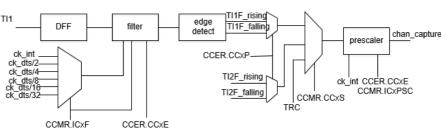

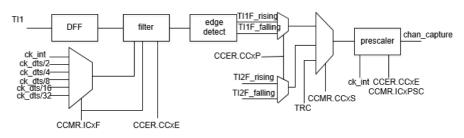

|     | 17.4.6. Capture/compare channels                              | 243 |

|     | 17.4.7. PWM mode                                              | 245 |

|     | 17.4.8. Channel output reference signal                       | 247 |

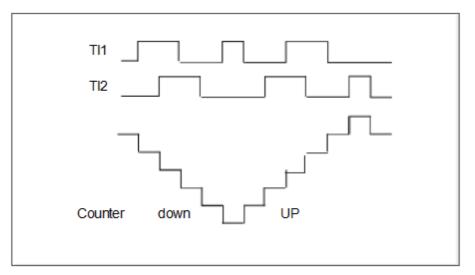

|     | 17.4.9. Quadrature decoder                                    | 248 |

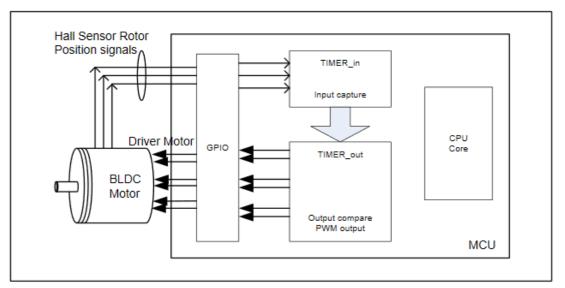

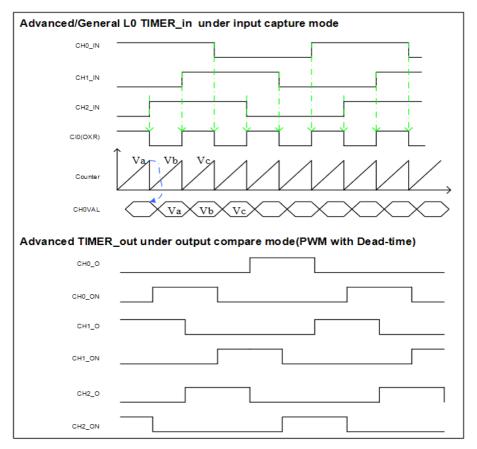

|     | 17.4.10. Hall sensor function                                 | 249 |

|     | 17.4.11. Single pulse mode                                    | 252 |

|     | 17.4.12. Timers interconnection                               | 252 |

|     | 17.4.13. Timer DMA mode                                       | 252 |

|     | 17.4.14. Timer debug mode                                     | 253 |

|     | 17.5. Register definition                                     | 253 |

|     | 17.5.1. Control register 1 (TIMx_CR1)                         | 253 |

|     | 17.5.2. Control register 2 (TIMx_CR2)                         | 254 |

|     | 17.5.3. Slave mode configuration register (TIMx_SMCR)         | 255 |

|     | 17.5.4. DMA and interrupt enable register (TIMx_DIER)         | 257 |

|     | 17.5.5. Interrupt flag register (TIMx_SR)                     | 258 |

|     | 17.5.6. Software event generation register (TIMx_EGR)         | 259 |

|     | 17.5.7. Channel control register 0 (TIMx_CCMR1)               | 259 |

|     | 17.5.8. Channel control register 1 (TIMx_CCMR2)               |     |

|     | 17.5.9. Channel control register 2 (TIMx_CCER)                | 264 |

|     | 17.5.10. Counter register (TIMx_CNT)                          | 265 |

|     | 17.5.11. Prescaler register (TIMx_PSC)                        | 265 |

|     | 17.5.12. Counter auto reload register (TIMx_ARR)              |     |

|     | 17.5.13. Channel 1 capture/compare value register (TIMx_CCR1) |     |

|     | 17.5.14. Channel 2 capture/compare value register (TIMx_CCR2) |     |

|     | 17.5.15. Channel 3 capture/compare value register (TIMx_CCR3) |     |

|     | 17.5.16. Channel 4 capture/compare value register (TIMx_CCR4) |     |

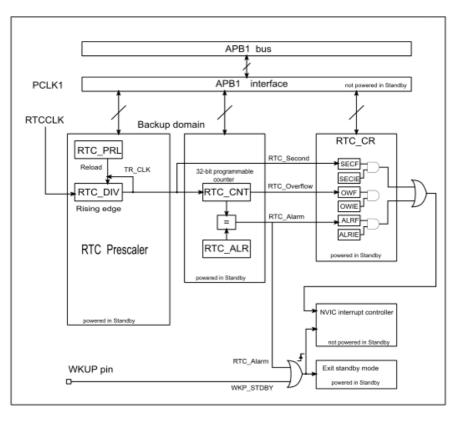

| 18. | Real-time Clock (RTC)                                         | 268 |

|     | 18.1. Overview                                                |     |

|     | 18.2. Characteristics                                         |     |

|     | 18.3. Function overview                                       |     |

|     | 18.3.1. RTC reset                                             | 269 |

|     | 18.3.2. RTC reading                                           | 269 |

|     | 18.3.3. RTC configuration                                     | 270 |

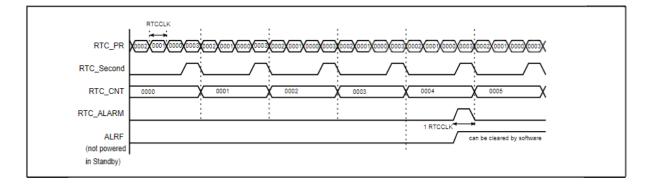

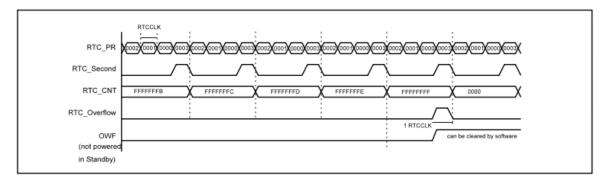

|     | 18.3.4. RTC flag assertion                                    | 270 |

|     | 18.4. Register definition                                     | 272 |

|     | 18.4.1. RTC interrupt enable register (RTC_CRH)               | 272 |

|     | 18.4.2. RTC control register (RTC_CRL)                        | 272 |

| 18.4.3. RTC prescaler high register (RTC_PRLH) | 273 |

|------------------------------------------------|-----|

| 18.4.4. RTC prescaler low register (RTC_PRLL)  |     |

| 18.4.5. RTC divider high register (RTC_DIVH)   | 273 |

| 18.4.6. RTC divider low register (RTC_DIVL)    | 274 |

| 18.4.7. RTC counter high register (RTC_CNTH)   | 274 |

| 18.4.8. RTC counter low register (RTC_CNTL)    | 274 |

| 18.4.9. RTC alarm high register (RTC_ALRH)     | 274 |

| 18.4.10. RTC alarm low register (RTC_ALRL)     | 274 |

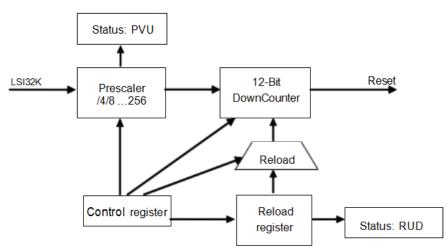

| 19. Watchdog timer (IWDG)                      | 276 |

| 19.1. Overview                                 | 276 |

| 19.2. Characteristics                          | 276 |

| 19.3. Function overview                        | 276 |

| 19.4. Register definition                      | 277 |

| 19.4.1. Control register (IWDG_KR)             |     |

| 19.4.2. Prescaler register (IWDG_PR)           | 278 |

| 19.4.3. Reload register (IWDG_RLR)             |     |

| 19.4.4. Status register (IWDG_SR)              | 278 |

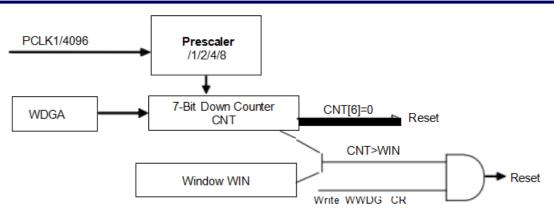

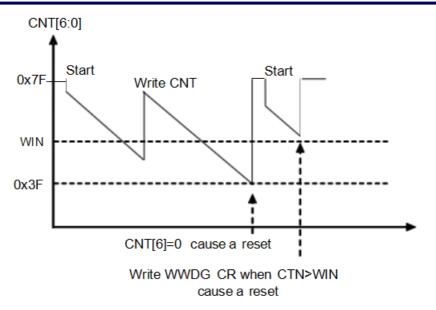

| 20. Window watchdog timer (WWDG)               | 280 |

| 20.1. Overview                                 |     |

| 20.2. Characteristics                          |     |

| 20.3. Function overview                        |     |

| 20.4. Register definition                      |     |

| 20.4.1. Control register (WWDG_CR)             |     |

| 20.4.2. Configuration register (WWDG_CFR)      |     |

| 20.4.3. Status register (WWDG_SR)              |     |

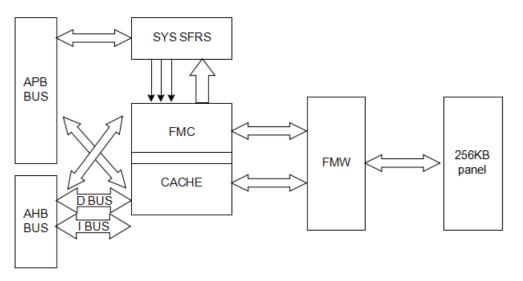

| 21. Flash controller (FMC)                     | 284 |

| 21.1. Flash controller overview                |     |

| 21.2. Major features of flash controller       |     |

| 21.3. Function description                     |     |

| 21.3.1. Write Operation                        |     |

| 21.3.2. CRC calculation                        |     |

| 21.4. Register definition                      |     |

| 21.4.1. CRC control register (FMC_CRCON)       |     |

| 21.4.2. Address register (FMC_ADDR)            |     |

| 21.4.3. Data register (FMC_DATA1)              |     |

| 21.4.4. Cache register (FMC_BUFx) x=063        |     |

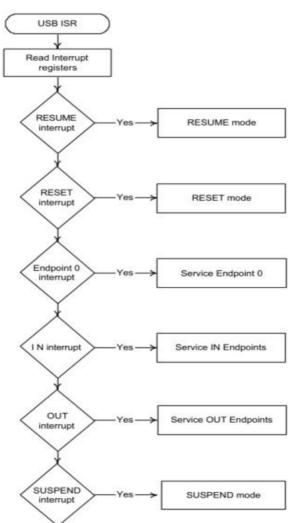

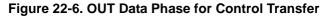

| 22. USB FULL SPEED DEVICE (USB)                | 287 |

| 22.1. USB introduction                         |     |

| 22.2. USB main features                        |     |

| 22.3. USB FIFO                                 |     |

| 22.4. Programming Scheme                       |     |

| 22.4.1. USB Interrupt Handling                 |     |

| 22.5. USB Reset                                |     |

| 22.6. Suspend/Resume                           |     |

|     | 22.6.1. USB modules active during suspend   | 289 |

|-----|---------------------------------------------|-----|

|     | 22.6.2. USB modules inactive during suspend |     |

|     | 22.6.3. Remote wake up                      |     |

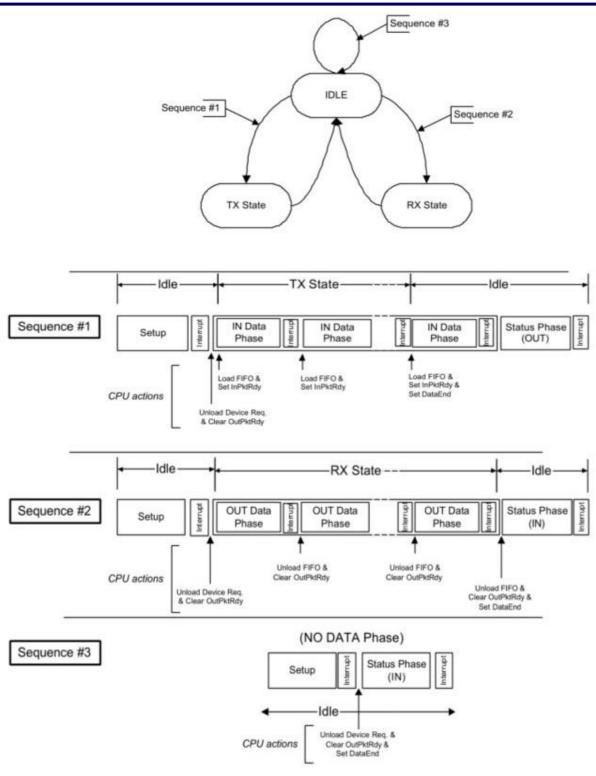

|     | 22.7. Endpoint 0 Handling                   |     |

|     | 22.7.1. Zero Data Requests                  |     |

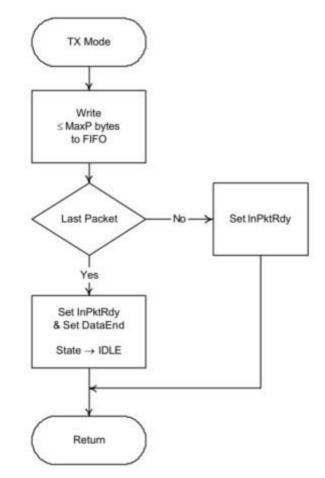

|     | 22.7.2. Write Requests                      |     |

|     | 22.7.3. Read Requests                       | 291 |

|     | 22.7.4. Endpoint 0 states                   | 292 |

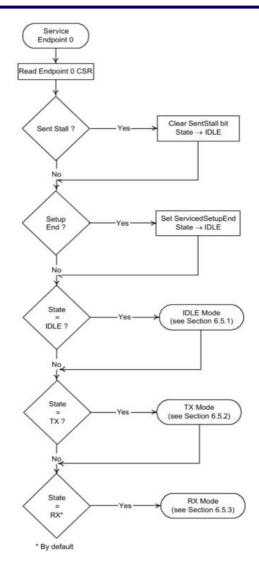

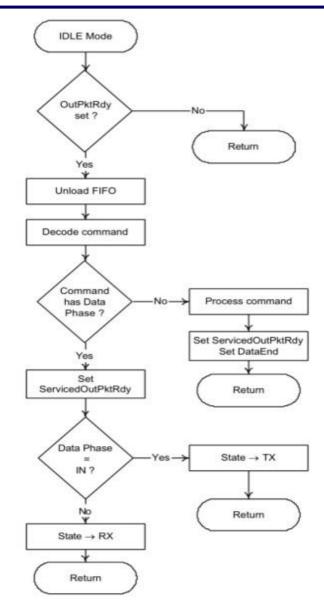

|     | 22.7.5. Endpoint 0 Service Routine          | 293 |

|     | 22.7.6. Error Handling                      | 298 |

|     | 22.8. Bulk IN Endpoint                      | 299 |

|     | 22.8.1. Setup Enpoint                       | 299 |

|     | 22.8.2. Enpoint Operation                   | 300 |

|     | 22.8.3. Error Handling                      | 300 |

|     | 22.9. Bulk OUT Endpoint                     | 300 |

|     | 22.9.1. Setup Enpoint                       | 301 |

|     | 22.9.2. Enpoint Operation                   | 301 |

|     | 22.9.3. Error Handling                      | 301 |

|     | 22.10. Interrupt In Endpoint                | 302 |

|     | 22.11. Interrupt Out Endpoint               | 302 |

|     | 22.12. Isochronous IN Endpoint              | 302 |

|     | 22.12.1. Setup Endpoint                     | 303 |

|     | 22.12.2. Enpoint Operation                  | 303 |

|     | 22.12.3. Error Handling                     | 304 |

|     | 22.13. Isochronous OUT Endpoint             | 304 |

|     | 22.13.1. Setup Enpoint                      | 304 |

|     | 22.13.2. Enpoint Operation                  | 305 |

|     | 22.13.3. Error Handling                     | 305 |

|     | 22.14. USB Registers                        | 305 |

|     | 22.14.1. USB Interrupt Registers            | 306 |

|     | 22.14.2. USB common register                | 309 |

|     | 22.14.3. USB Frame Number Registers         |     |

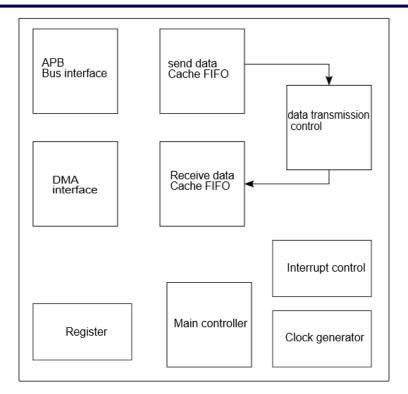

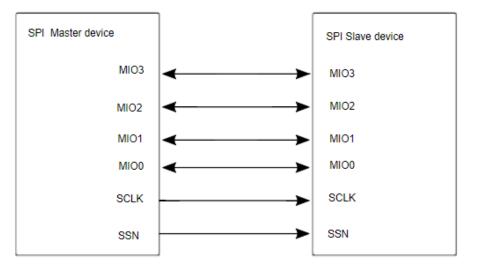

| 23. | Serial peripheral interface (SPI)           | 316 |

|     | 23.1. Introduction                          | 316 |

|     | 23.2. SPI features                          | 316 |

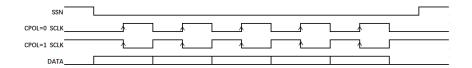

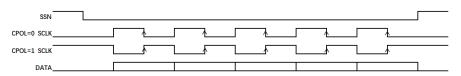

|     | 23.3. Clock mode                            | 317 |

|     | 23.4. Transfer Modes                        | 318 |

|     | 23.5. SPI slave mode                        | 319 |

|     | 23.6. SPI master mode                       | 321 |

|     | 23.7. DMA transmission                      | 324 |

|     | 23.8. Interrupts                            | 324 |

|     | 23.9. SPI Slave mode register               |     |

|     | 23.9.1. SPI Control register 0(SPI_CR0)     |     |

|     | 23.9.2. SPI Enable register (SPI_SPIENR)    | 326 |

| 23.9.3. MICROWIRE Control register (SPI_MWCR)                    |     |

|------------------------------------------------------------------|-----|

| 23.9.4. TX FIFO threshold register (SPI_TXFTLR)                  |     |

| 23.9.5. Receive FIFO threshold register (SPI_RXFTLR)             |     |

| 23.9.6. TX FIFO status register (SPI_TXFLR)                      |     |

| 23.9.7. Receive FIFO status register (SPI_RXFLR)                 |     |

| 23.9.8. SPI Status register (SPI_SR)                             |     |

| 23.9.9. Interrupt enable register (SPI_IER)                      |     |

| 23.9.10. Interrupt status register (SPI_ISR)                     |     |

| 23.9.11. Raw interrupt status register (SPI_RISR)                |     |

| 23.9.12. Transmit Overflow interrupt clear register (SPI_TXOICR) |     |

| 23.9.13. Receive Overflow interrupt clear register (SPI_RXOICR)  |     |

| 23.9.14. Receive underflow interrupt clear register (SPI_RXUICR) |     |

| 23.9.15. Interrupt clear register (SPI_ICR)                      |     |

| 23.9.16. DMA ENABLE register (SPI_DMACR)                         |     |

| 23.9.17. DMA TX threshold register (SPI_DMATDLR)                 |     |

| 23.9.18. DMA RX threshold register (SPI_DMARDLR)                 |     |

| 23.9.19. SPI Data register (SPI_DR)                              |     |

| 23.10. SPI master mode register                                  |     |

| 23.10.1. SPI Control register0 (SPI_CR0)                         | 331 |

| 23.10.2. SPI Control Register 1(SPI_CR1)                         | 332 |

| 23.10.3. SPI Enable Register (SPI_SPIENR)                        | 332 |

| 23.10.4. MICROWIRE Control Register (SPI_MWCR)                   |     |

| 23.10.5. Slave Select Register (SPI_SER)                         | 333 |

| 23.10.6. Baud Rate Register (SPI_BAUDR)                          |     |

| 23.10.7. TX FIFO Threshold Register (SPI_TXFTLR)                 | 334 |

| 23.10.8. RX FIFO Threshold Register (SPI_RXFTLR)                 |     |

| 23.10.9. TX FIFO Status Register (SPI_TXFLR)                     |     |

| 23.10.10. RX FIFO Status Register (SPI_RXFLR)                    |     |

| 23.10.11. SPI Status Register (SPI_SR)                           |     |

| 23.10.12. Interrupt enable register (SPI_IER)                    |     |

| 23.10.13. Interrupt status register (SPI_ISR)                    |     |

| 23.10.14. Raw interrupt status register (SPI_RISR)               |     |

| 23.10.15. Overflow interrupt clear register (SPI_TXOICR)         |     |

| 23.10.16. RX Overflow interrupt clear register (SPI_RXOICR)      |     |

| 23.10.17. RX underflow interrupt clear register (SPI_RXUICR)     | 336 |

| 23.10.18. Interrupt clear register (SPI_ICR)                     |     |

| 23.10.19. DMA Enable register (SPI_DMACR)                        |     |

| 23.10.20. DMA TX threshold register (SPI_DMATDLR)                |     |

| 23.10.21. DMA RX threshold register (SPI_DMARDLR)                |     |

| 23.10.22. SPI Data register (SPI_DR)                             |     |

| . 4-wire serial peripheral interface (QSPI)                      |     |

| 24.1. Introduction                                               |     |

| 24.2. QSPI features                                              | 340 |

| 24.3. Clock phase and clock polarity                             |     |

|                                                                  |     |

24.

| 24.4. Transfer Modes                                              | 341 |

|-------------------------------------------------------------------|-----|

| 24.5. QSPI Master Mode                                            | 341 |

| 24.6. DMA transmission                                            | 342 |

| 24.7. Interrupt                                                   | 342 |

| 24.8. QSPI Master Mode Register                                   | 343 |

| 24.8.1. QSPI Control Register 0(QSPI_CR0)                         | 343 |

| 24.8.2. QSPI Control register 1(QSPI_CR1)                         | 344 |

| 24.8.3. QSPI Enable register (QSPI_SPIENR)                        | 344 |

| 24.8.4. Slave select register (QSPI_SER)                          | 344 |

| 24.8.5. Baud rate register (QSPI_BAUDR)                           | 344 |

| 24.8.6. TX FIFO threshold register (QSPI_TXFTLR)                  | 345 |

| 24.8.7. RX FIFO threshold register (QSPI_RXFTLR)                  | 345 |

| 24.8.8. TX FIFO status register (QSPI_TXFLR)                      | 345 |

| 24.8.9. RX FIFO status register (QSPI_RXFLR)                      | 345 |

| 24.8.10. QSPI Status register (QSPI_SR)                           | 346 |

| 24.8.11. Interrupt enable register (QSPI_IER)                     | 346 |

| 24.8.12. Interrupt status register (QSPI_ISR)                     | 346 |

| 24.8.13. Raw interrupt status register (QSPI_RISR)                |     |

| 24.8.14. TX overflow interrupt clear register (QSPI_TXOICR)       | 347 |

| 24.8.15. RX overflow interrupt clear register (QSPI_RXOICR)       | 347 |

| 24.8.16. Receive underflow interrupt clear register (QSPI_RXUICR) | 348 |

| 24.8.17. Interrupt clear register (QSPI_ICR)                      | 348 |

| 24.8.18. DMA Enable register (QSPI_DMACR)                         | 348 |

| 24.8.19. DMA TX threshold register (QSPI_DMATDLR)                 | 348 |

| 24.8.20. DMA RX threshold register (QSPI_DMARDLR)                 | 349 |

| 24.8.21. QSPI Data register (QSPI_DR)                             | 349 |

| 24.8.22. QSPI Enhanced mode configuration register (QSPI_ESPICR)  | 349 |

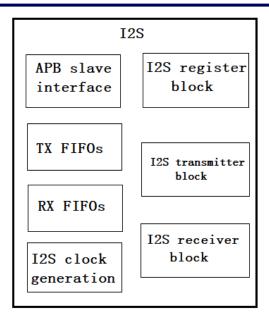

| 25. Inter-IC Sound Bus (I2S)                                      | 351 |

| 25.1. I2S Introduction                                            | 351 |

| 25.2. I2S Main Features                                           | 351 |

| 25.3. I2S Functional Description                                  | 351 |

| 25.3.1. Block Diagram                                             | 351 |

| 25.3.2. I2S transport protocols                                   | 352 |

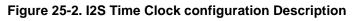

| 25.3.3. I2S clock configuration                                   | 352 |

| 25.3.4. I2S Enable                                                | 353 |

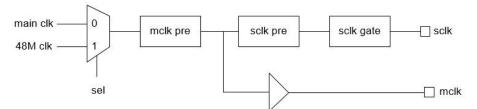

| 25.3.5. Transmit Mode                                             | 353 |

| 25.3.6. Receiver mode                                             | 354 |

| 25.3.7. Interrupt                                                 | 356 |

| 25.4. Register Description                                        | 357 |

| 25.4.1. I2S Enable Register (I2S_IER)                             | 357 |

| 25.4.2. I2S Receiver Block Enable Register (I2S_IRER)             | 357 |

| 25.4.3. I2S Transmitter Block Enable Register (I2S_ITER)          | 358 |

| 25.4.4. Clock Enable Register (I2S_CER)                           | 358 |

| 25.4.5. Clock Configuration Register (I2S_CCR)                    | 358 |

|     | 25.4.6. Receiver Block FIFO Reset Register (I2S_RXFFR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 358                                                                                                                                                                                                                                                                                                                                                 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | 25.4.7. Transmitter Block FIFO Reset Register (I2S_TXFFR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 359                                                                                                                                                                                                                                                                                                                                                 |

|     | 25.4.8. Left Receive Buffer Register x (I2S_LRBRx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 359                                                                                                                                                                                                                                                                                                                                                 |

|     | 25.4.9. Left Transmit Holding Register x (I2S_LTHRx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 359                                                                                                                                                                                                                                                                                                                                                 |

|     | 25.4.10. Right Receive Buffer Register x (I2S_RRBRx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 359                                                                                                                                                                                                                                                                                                                                                 |

|     | 25.4.11. Right Transmit Holding Register x (I2S_RTHRx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 359                                                                                                                                                                                                                                                                                                                                                 |

|     | 25.4.12. Receive Enable Register x (I2S_RERx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.13. Transmit Enable Register x (I2S_TERx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.14. Receive Configuration Register x (I2S_RCRx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.15. Channel Configuration Register For TX (I2S_TCRx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.16. Channel Interrupt Status Register x (I2S_ISRx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.17. Channel Interrupt Mask Register x (I2S_IMRx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 361                                                                                                                                                                                                                                                                                                                                                 |

|     | 25.4.18. Receive Overrun Register x (I2S_RORx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.19. Transmit Overrun Register x (I2S_TORx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.20. Receive FIFO Configuration Register x (I2S_RFCRx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.21. Transmit FIFO Configuration Register x (I2S_TFCRx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.22. Receive FIFO Flush Register x (I2S_RFFx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.23. Transmit FIFO Flush Register x (I2S_TFFx x=0,1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.24. Receiver Block DMA Register (I2S_RXDMA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.25. Reset RX DMA Register (I2S_RRXDMA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.26. Transmitter Block DMA Register (I2S_TXDMA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                     |

|     | 25.4.27. Reset Transmitter Block DMA Register (I2S_RTXDMA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                     |

|     | <b>5</b> ( <b>1</b> <i>)</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                     |

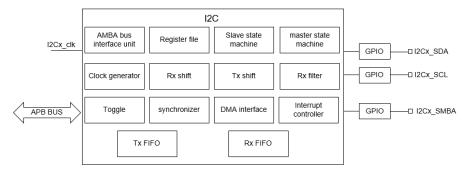

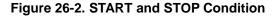

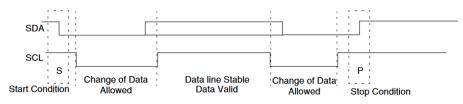

| 26. | Integrated Circuit Interface (I2C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                     |

| 26. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 365                                                                                                                                                                                                                                                                                                                                                 |

| 26. | Integrated Circuit Interface (I2C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>365</b><br>365                                                                                                                                                                                                                                                                                                                                   |

| 26. | Integrated Circuit Interface (I2C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                     |

| 26. | Integrated Circuit Interface (I2C)<br>26.1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                     |